# aSLC MicroSDHC Card 3.0

# **PHANES-F Series**

Document No. : 100-xPMSD-PFITMBAS

Version No.: 03V0

Date : December, 2022

ISO 9001 : 2015 CERTIFIED

# Product Features

#### Flash IC

- Samsung 14nm NAND Flash IC.

- Multi-Level Cell (MLC) management by enhance endurance technology (aSLC)

#### Compatibility

- SD Memory Card Specifications, Part 1 Physical Layer Specification, version 3.1 Final

- SD Memory Card Specifications, Part 3, Security Specification, Version 3.0 Final

#### Additional Capabilities

- S.M.A.R.T.\*<sup>1</sup> (Self-Monitoring, Analysis and Reporting Technology) feature set support.

- Supports SD command Class 2/4/6/10

- Supports UHS-1

- Supports SD mode and SPI mode

- Supports CPRM

- Supports Embedded Mode

- Support bad Block Management

- Support both Static and Dynamic Wear Leveling

#### Mechanical

- 8 exposed contact pins on one side.

- Dimension: 15.0mm x 11.0mm x 1.0mm.

- Weight: 0.3 g / 0.01 oz.

#### Power Operating Voltage 2.7V to 3.6V

- Read Mode: 400 mA (max.)

- Write Mode: 400 mA (max.)

- Standby Mode: 1000 uA (max.)

#### Performance (Maximum value) \*<sup>2</sup>

- Seq. Read: 95.3 MB/sec. (Kioxia 32GB.)

- Seq. Write: 83.6 MB/sec. (Kioxia 32GB.)

- Seq. Read: 95.0 MB/sec. (Samsung 16GB.)

- Seq. Write: 85.0 MB/sec. (Samsung 16GB.)

#### Capacity

4GB, 8GB and 16GB

#### Reliability

- ECC: Designed with BCH ECC Algorithm.

- **MTBF:** > 3,000,000 hours

- Temperature: (Operating)

Standard Grade: 0°C ~ +70°C

Wide Temp. Grade: -40°C ~ +85°C

- Vibration: 80Hz~2000Hz/20G.

- Shock: 0.5ms, 1500 G, 3 axes.

- Erase counts: 20K

#### Certifications and Declarations

- Certifications: CE & FCC

- Declarations: RoHS & REACH

#### Remarks:

- 1. Support official S.M.A.R.T. Utility.

- Sequential performance is based on CrystalDiskMark

5.1.2 with file size 1000MB

# **Order Information**

- I. Part Number List

- ♦ APRO aSLC Micro Secure Digital Memory Card PHANES-F Series

| Product Picture | Grade | Wide Temp Grade(-40°C ~ +85°C) |

|-----------------|-------|--------------------------------|

|                 | 4GB   | WPMSD004G-PFISMAS              |

| APRO Co., Ltd.  | 8GB   | WPMSD008G-PFISMAS              |

|                 | 16GB  | WPMSD016G-PFISMAS              |

|                 | 32GB  | -                              |

#### II. Part Number Decoder:

# X1 X2 X3 X4 X5 X6 X7 X8 X9–X11 X12 X13 X14 X15 X16 X17 X18

| X1 : Grade   | •             |                 |                  |   |

|--------------|---------------|-----------------|------------------|---|

| W: Wide Te   | mp Grade- o   | perating temp.  | -40° C ~ +85 ° C |   |

|              |               |                 |                  |   |

| X2 : The m   | naterial of c | ase             |                  |   |

| P: Plastic c | asing         |                 |                  | 1 |

|              |               |                 |                  |   |

| X3 X4 X5     | : Product ca  | ategory         |                  |   |

| MSD : Micro  | o Secure Digi | ital (SD) memor | y card           | 9 |

|              |               |                 |                  |   |

| X6 X7 X8     | X9 : Capaci   | ty              |                  |   |

| 004G:        | 4GB           | 016G:           | 16GB             | I |

| 008G:        | 8GB           |                 |                  |   |

|              |               |                 |                  |   |

| X11 : Cont   | roller        |                 |                  | I |

| P: PHANES    | Series        |                 |                  |   |

|              |               |                 |                  |   |

|              |               |                 |                  |   |

X12 : Controller version

А, В, С.....

X13 : Controller Grade I : Industrial grade

X14 : Flash IC S : Samsung NAND Flash IC

X15 : Flash IC grade / Type M : MLC – NAND Flash IC

X16 : Flash IC B : Samsung 14nm MLC

## X17 X18 : Flash IC grade / Type

AS : aSLC Technology extends MLC product's lifespan

# **Revision History**

| Revision | Description                                                                                 | Date       |

|----------|---------------------------------------------------------------------------------------------|------------|

| 1.0      | Initial release                                                                             | 2016/04/25 |

| 2.0      | Updated performance                                                                         | 2019/04/01 |

| 2.1      | Updated Document form                                                                       | 2019/06/17 |

| 2.2      | Add. Samsung Solution                                                                       | 2021/05/14 |

| 2.3      | Correct description:<br>Supply Voltage: 3.3V(+/-) 10%<br>to<br>Supply Voltage: 2.7V to 3.6V | 2021/07/9  |

| 3.0      | Remove Toshiba solution                                                                     | 2022/12/22 |

# <u>Contents</u>

| Pro | duct l | Features 2 -                                                            |

|-----|--------|-------------------------------------------------------------------------|

| Ord | ler In | formation 3 -                                                           |

|     | I.     | Part Number List 3 -                                                    |

|     | II.    | Part Number Decoder: 3 -                                                |

| Rev | rision | History 4 -                                                             |

| Con | itents | 5 5 -                                                                   |

| 1.  |        | Introduction 6 -                                                        |

|     | 1.1    | <b>. Scope</b> 6 -                                                      |

|     | 1.2    | <i>Flash Management Technology – Static &amp; Dynamic Wear Leveling</i> |

|     | 1.3    | Bad Block Management 6 -                                                |

|     | 1.4    | Embedded Mode 6 -                                                       |

|     | 1.5    | - 7 -                                                                   |

| 2.  |        | Product Specifications 7 -                                              |

|     | 2.1    | System Environmental Specifications 7 -                                 |

|     | 2.2    | System Power Requirements 8 -                                           |

|     | 2.3    | System Performance 8 -                                                  |

|     | 2.4    | System Reliability 8 -                                                  |

|     | 2.5    | Physical Specifications 9 -                                             |

| З.  |        | Interface Description 11 -                                              |

|     | 3.1    | Micro Secure Digital Memory Card interface 11 -                         |

|     | 3.2    | Pin Assignments 11 -                                                    |

| Ap  | bend   | ix A: Limited Warranty 12 -                                             |

### 1. Introduction

APRO aSLC Micro Secure Digital Memory Card PHANES-F Series is specifically designed to meet the security, performance and environmental requirements of some significant applications such like networking, telecommunications and data-communications, mobile & embedded computing, medical instruments and industrial computing applications.

The main used Flash memory is aSLC-NAND Type Flash memory chips are 4GB, 8GB and 16GB. APRO aSLC Micro Secure Digital Memory Card PHANES-F Series include a copyright protection that complies with the security of the SDMI standard, and the physical form-factor, pin assignment.

### 1.1. Scope

This document describes the key features and specifications of APRO aSLC Micro Secure Digital Memory Card PHANES-F Series.

## 1.2. Flash Management Technology – Static & Dynamic Wear Leveling

NAND flash devices can only undergo a limited number of program/erase cycles, and in most cases, the flash media are not used evenly. If some areas get updated more frequently than others, the lifetime of the device would be reduced significantly. Thus, Wear Leveling is applied to extend the lifespan of NAND Flash by evenly distributing write and erase cycles across the media.

APRO aSLC Micro Secure Digital Memory Card PHANES-F Series provides advanced Wear Leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. Moreover, by implementing both dynamic and static Wear Leveling algorithms, the life expectancy of the NAND flash is greatly improved.

### 1.3. Bad Block Management

#### > Early Bad Block

The fault block generated during the manufacturing process of NAND Flash is called Early Bad Block.

#### Later Bad Block

In the process of use, as the number of operations of writing and erasing increases, a fault block is gradually generated, which is called a Latter Bad Block.

**Bad block management** is a management mechanism for a bad block to be detected by the control IC and mark bad blocks in the NAND Flash and improve the reliability of data access. The bad block management mechanism of the control IC will establish a **Bad Block Table** when the NAND Flash is started for the first time, and will also record the errors found in the process of use in the bad block table, and data is ported to new valid blocks to avoid data loss.

In order to detect the initial bad blocks to handle run time bad blocks, APRO aSLC Micro Secure Digital Memory Card PHANES-F Series provides the **Bad Block Management** scheme. It remaps a bad block to one of the reserved blocks so that the data contained in one bad block is not lost and new data writes on a bad block is avoided.

## 1.4. Embedded Mode

Embedded mode is a function specially designed for operating systems that do not utilize FAT. Often under non Windows OS, for example Linux or customized host, wear leveling mechanism of APRO aSLC MicroSD cards will be affected or even disabled in some cases. With embedded mode activated, aSLC MicroSD cards ensure that under any circumstances, wear leveling mechanism can operate normally to keep the usage of blocks even throughout the MicroSD card's life cycle. This is especially a great add-on for security cameras or drive recorders.

### 1.5. aSLC Technology

The aSLC can be considered as an extended version of the MLC. While MLC contains both fast and slow pages, aSLC only utilizes fast pages for programming. The concept of aSLC is demonstrated in the Figure 2 below. The first and second bits of a memory cell represent a fast and slow page respectively, as shown in the left table. Since only fast pages are programmed when applying aSLC, the bits highlighted in red are used, as shown in the right table. As a result, aSLC provides better performance and endurance than MLC does. Moreover, the aSLC performs similarly to the SLC, yet more cost effective

| MLC                        | Flash                      |               | aSLC                       | C Flash                    |

|----------------------------|----------------------------|---------------|----------------------------|----------------------------|

| 1 <sup>st</sup> bit (fast) | 2 <sup>nd</sup> bit (slow) |               | 1 <sup>st</sup> bit (fast) | 2 <sup>nd</sup> bit (slow) |

| 1                          | 1                          |               | 1                          | 1                          |

| 1                          | 0                          | $\rightarrow$ | 1                          | 0                          |

| 0                          | 1                          |               | 0                          | 1                          |

| 0                          | 0                          |               | 0                          | 0                          |

#### Figure 1: The concept of APRO aSLC technology

### 2. Product Specifications

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

## 2.1. System Environmental Specifications

| APRO aSLC Micro Secure Digital Memory Card<br>PHANES-F Series |                            | Wide temp Grade          |  |

|---------------------------------------------------------------|----------------------------|--------------------------|--|

| Tomporatura                                                   | Operating:                 | -40°C ~ +85°C            |  |

| Temperature                                                   | Non-operating:             | -50°C ~ +95°C            |  |

| Humidity                                                      | Operating & Non-operating: | 10% ~ 95% non-condensing |  |

| Vibration                                                     | Operating & Non-operating: | 80Hz~2000Hz/20G.         |  |

| Shock                                                         | Operating & Non-operating: | 0.5ms, 1500 G, 3 axes    |  |

### 2.2. System Power Requirements

#### Table 2: Power Requirement

| APRO aSLC Micro Secure Digital Memory Card PHANES-F Series |                                             | Wide temp Grade          |  |

|------------------------------------------------------------|---------------------------------------------|--------------------------|--|

| DC Input Voltage (VCC)                                     |                                             | 2.7V to 3.6V             |  |

|                                                            | Reading Mode :      400 mA (UHS-I Mode max. |                          |  |

| Maximum average value                                      | Writing Mode :                              | 400 mA (UHS-I Mode max.) |  |

|                                                            | Standby Mode :                              | 1000 uA (max.)           |  |

### 2.3. System Performance

Table 3: System Performances

| Data Transfer Mode supporting |                         | SDA Specification Ver 3.0 |      |      |

|-------------------------------|-------------------------|---------------------------|------|------|

| Average Access Time           |                         | 1 ms (estimated)          |      |      |

| Flash Capacity                |                         | 4GB                       | 8GB  | 16GB |

| Comoura                       | Sequential Read (MB/s)  | 90.0                      | 95.0 | 95.0 |

| Samsung                       | Sequential Write (MB/s) | 80.0                      | 80.0 | 85.0 |

Note:

$\succ\,$  All values quoted are typically at 25  ${}^\circ\!\!{}^\circ\!\!{}^\circ$  and nominal supply voltage.

> The performance is obtained from TestMetrix Test (@500MB).

## 2.4. System Reliability

#### Table 4: System Reliability

| Wear-leveling Algorithms        | Static and Dynamic wear-leveling algorithms                              |  |  |

|---------------------------------|--------------------------------------------------------------------------|--|--|

| Bad Blocks Management           | Supportive                                                               |  |  |

| ECC Technology                  | BCH ECC                                                                  |  |  |

| МТВБ                            | > 3,000,000 hours                                                        |  |  |

| Endurance                       | NAND MLC Flash w/aSLC Technology : 20K Erase counts                      |  |  |

| Durability                      | 10,000 inserting cycles                                                  |  |  |

| Bending                         | >10N                                                                     |  |  |

| Torque                          | 0.1N +/- 2.5 deg.                                                        |  |  |

| Drop Test                       | 1.5M free fall                                                           |  |  |

| Salt Spray                      | Concentration: 3% NaCl/35°C                                              |  |  |

| Waterproof                      | 1000mm submerge for 30 minutes, IPx7 compliance                          |  |  |

| Flacture static Dischause (FCD) | Contact: +/- 4KV each item 5 times                                       |  |  |

| Electrostatic Discharge (ESD)   | Air: +/- 8KV 5 times                                                     |  |  |

| V. Day Expecting Test           | 0.1 Gy of medium energy radiation (70 keV to 140keV, cumulative does per |  |  |

| X-Ray Exposure Test             | year) to both sides of the card.                                         |  |  |

Note:

> The endurance of SSD could be estimated based on user behavior, NAND endurance cycles, and write amplification factor.

It is not guaranteed by flash vendor.

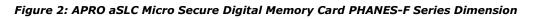

## 2.5. Physical Specifications

Refer to Table 5 and see Figure 1 for aSLC Micro Secure Digital Memory Card PHANES-F Series physical specifications and dimensions.

#### Table 5: Physical Specifications of APRO aSLC Micro Secure Digital Memory Card PHANES-F Series

| Length:    | 15.00 mm        |

|------------|-----------------|

| Width:     | 11.00 mm        |

| Thickness: | 1.0 mm          |

| Weight:    | 0.3 g / 0.01 oz |

|        | COMMON       | DIMENS | IONS  |       |

|--------|--------------|--------|-------|-------|

| SYMBOL | MIN          | NOM    | MAX   | NOTE  |

| A      | 10.90        | 11.00  | 11.10 |       |

| A1     | 9.60         | 9.70   | 9.80  |       |

| A2     | -            | 3.85   | -     | BASIC |

| A3     | 7.60         | 7.70   | 7.80  |       |

| A4     | -            | 1.10   | -     | BASIC |

| A5     | 0.75         | 0.80   | 0.85  |       |

| A6     | 8 <b>-</b> 9 | -      | 8.50  |       |

| A7     | 0.90         | -      | 2-2   |       |

| A8     | 0.60         | 0.70   | 0.80  |       |

| A9     | 0.80         | -      | -     |       |

| В      | 14.90        | 15.00  | 15.10 |       |

| B1     | 6.30         | 6.40   | 6.50  |       |

| B2     | 1.64         | 1.84   | 2.04  |       |

| B3     | 1.30         | 1.50   | 1.70  |       |

| B4     | 0.42         | 0.52   | 0.62  |       |

| B5     | 2.80         | 2.90   | 3.00  |       |

| B6     | 5.50         | -      | 240   |       |

| B7     | 0.20         | 0.30   | 0.40  |       |

| B8     | 1.00         | 1.10   | 1.20  |       |

| B9     |              | -      | 9.00  |       |

| B10    | 7.80         | 7.90   | 8.00  |       |

| B11    | 1.10         | 1.20   | 1.30  |       |

| С      | 0.90         | 1.00   | 1.10  |       |

| C1     | 0.60         | 0.70   | 0.80  |       |

| C2     | 0.20         | 0.30   | 0.40  |       |

| C3     | 0.00         | -      | 0.15  |       |

| D1     | 1.00         | -      | -     |       |

| D2     | 1.00         | -      | -     |       |

| D3     | 1.00         | -      |       |       |

| R1     | 0.20         | 0.40   | 0.60  |       |

| R2     | 0.20         | 0.40   | 0.60  |       |

| R3     | 0.70         | 0.80   | 0.90  |       |

| R4     | 0.70         | 0.80   | 0.90  |       |

| R5     | 0.70         | 0.80   | 0.90  |       |

| R6     | 0.70         | 0.80   | 0.90  |       |

| R7     | 29.50        | 30.00  | 30.50 |       |

| R10    | -            | 0.20   | -     |       |

| R11    | -            | 0.20   | -     |       |

| R17    | 0.10         | 0.20   | 0.30  |       |

| R18    | 0.20         | 0.40   | 0.60  |       |

| R19    | 0.05         | -      | 0.20  |       |

Notes:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 2. DIMENSIONS ARE IN MILLIMETERS.

- 3. COPLANARITY IS ADDITIVE TO C1 MAX THICKNESS.

# 3. Interface Description

# 3.1. Micro Secure Digital Memory Card interface

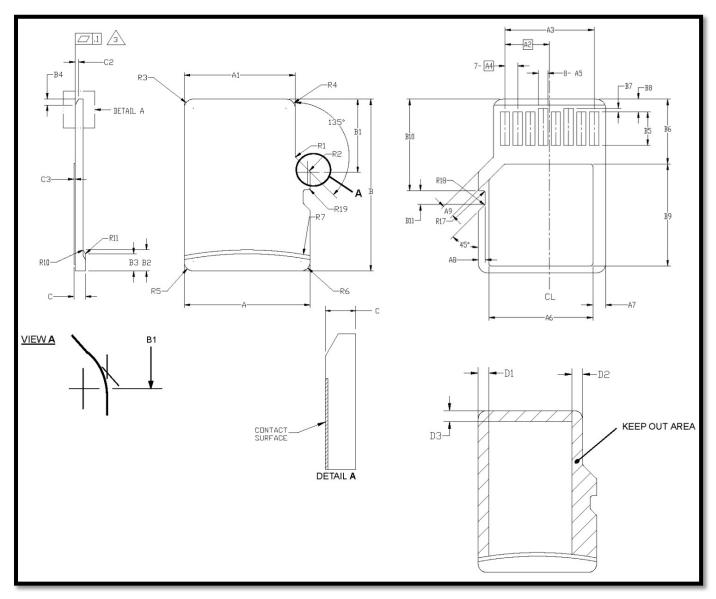

APRO aSLC Micro Secure Digital Memory Card PHANES-F Series has eight exposed contacts on one side.

Figure 3: 8 Pins Connector

## 3.2. Pin Assignments

There are total of 8 pins in the Micro SD Connector. The pin assignments are listed in below table 6.

| Pin Number | SD Mode                |                     |                                | SPI Mode        |       |                       |

|------------|------------------------|---------------------|--------------------------------|-----------------|-------|-----------------------|

|            | Pin Name               | Type <sup>1</sup>   | Description                    | Pin Name        | Туре  | Description           |

| Pin 1      | DAT2                   | I/O/PP              | Data Line [bit2]               | RSV             |       |                       |

| Pin 2      | CD / DAT3 <sup>2</sup> | I/O/PP <sup>3</sup> | Card Detect / Data Line [bit3] | CS              | $I^3$ | Chip Select           |

| Pin 3      | CMD                    | РР                  | Command / Response             | DI              | Ι     | Data in               |

| Pin 4      | V <sub>DD</sub>        | S                   | Supply voltage                 | V <sub>DD</sub> | S     | Supply voltage        |

| Pin 5      | CLK                    | Ι                   | Clock                          | SCLK            | Ι     | Clock                 |

| Pin 6      | V <sub>ss</sub>        | S                   | Supply voltage ground          | V <sub>SS</sub> | S     | Supply voltage ground |

| Pin 7      | DAT0                   | I/O/PP              | Data Line [bit0]               | DO              | O/PP  | Data Out              |

| Pin 8      | DAT1                   | I/O/PP              | Data Line [bit1]               | RSV             |       |                       |

```

Table 6 - Pin Assignments

```

- S: power supply, I:input; O:output using push-pull drivers; PP:I/O using push-pull drivers.

- The extended DAT lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after SET\_BUS\_WIDTH command. The Host shall keep its own DAT1-DAT3 lines in input mode, as well, while they are not used. It is defined so, in order to keep compatibility to Multi-Media Cards.

- At power up this line has a 50KOhm pull up enabled in the card. This resistor serves two functions Card detection and Mode Selection. For Mode Selection, the host can drive the line high or let it be pulled high to select SD mode. If the host wants to select SPI mode it should drive the line low. For Card detection, the host detects that the line is pulled high. This pull-up should be disconnected by the user during regular data transfer period, withSET\_CLR\_CARD\_DETECT(ACMD42) command.

## Appendix A: Limited Warranty

APRO warrants your aSLC Micro Secure Digital Memory Card PHANES-F Series against defects in material and workmanship for the life of the drive. The warranty is void in the case of misuse, accident, alteration, improper installation, misapplication or the result of unauthorized service or repair. The implied warranties of merchantability and fitness for a particular purpose, and all other warranties, expressed or implied, except as set forth in this warranty, shall not apply to the products delivered. In no event shall APRO be liable for any lost profits, lost savings or other incidental or consequential damages arising out of the use of, or inability to use, this product.

#### BEFORE RETURNING PRODUCT, A RETURN MATERIAL AUTHORIZATION (RMA) MUST BE OBTAINED FROM APRO.

Product shall be returned to APRO with shipping prepaid. If the product fails to conform based on customers' purchasing orders, APRO will reimburse customers for the transportation charges incurred.

#### WARRANTY PERIOD:

• aSLC (Standard grade / Wide temp. grade ) 2 years / Within 20K Erasing Counts

This document is for information use only and is **subject to change without prior notice**. APRO Co., Ltd. assumes no responsibility for any errors that may appear in this document, nor for incidental or consequential damages resulting from the furnishing, performance or use of this material. No part of this document may be reproduced, transmitted, transcribed, stored in a retrievable manner or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written consent of an officer of APRO Co., Ltd.

All parts of the APRO documentation are protected by copyright law and all rights are reserved.

APRO and the APRO logo are registered trademarks of APRO Co., Ltd.

Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

© 2022 APRO Corporation. All rights reserved