## **PCI-1758U Series**

128-Channel Isolated Digital Input/Output Card

**User Manual**

#### Copyright

The documentation and the software included with this product are copyrighted 2005 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

#### Acknowledgements

PC-LabCard is a trademark of Advantech Co., Ltd. IBM and PC are trademarks of International Business Machines Corporation. MS-DOS, Windows®, Microsoft® Visual C++ and Visual BASIC are trademarks of Microsoft® Corporation. Intel® and Pentium® are trademarks of Intel Corporation. Delphi and C++ Builder are trademarks of Inprise Corporation.

Part No. 2003175801 2nd Edition

Printed in Taiwan May 2005

#### **Product Warranty (2 years)**

Advantech warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Advantech, or which have been subject to misuse, abuse, accident or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain an RMA (return merchandize authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

#### CE

All products in the PCI-1758U Series have passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### **Technical Support and Assistance**

- Step 1. Visit the Advantech web site at **www.advantech.com/support** where you can find the latest information about the product.

- Step 2. Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Please have the following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

#### **Packing List**

Before setting up the system, check that the items listed below are included and in good condition. If any item does not accord with the table, please contact your dealer immediately.

The PCI-1758U include the following items:

1 x PCI-1758UDI, PCI-1758UDO or PCI-1758UDIO card

1 x Companion CD-ROM (DLL driver included)

1 x User Manual (This manual)

## Contents

| Chapter  | 1   | General Information                                                                            | . 2        |

|----------|-----|------------------------------------------------------------------------------------------------|------------|

| -        | 1.1 | Introduction                                                                                   |            |

|          |     | Table 1.1:PCI-1758U Series Features Comparison                                                 |            |

|          | 1.2 | Installation Guide                                                                             | 6          |

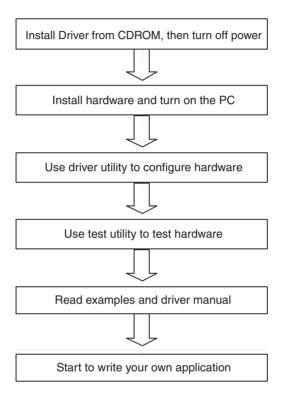

|          | 1.0 | Figure 1.1:Installation Flow Chart                                                             |            |

|          | 1.3 | Accessories                                                                                    | 8<br>8     |

|          |     | 1.3.2 ADAM-39100 Wiring Terminal Board                                                         |            |

| Chapter  | 2   | Installation                                                                                   |            |

| <b>I</b> | 2.1 | Unpacking                                                                                      |            |

|          | 2.2 | Driver Installation                                                                            | . 11       |

|          |     | Figure 2.1:The Setup Screen of Advantech Automatio                                             | n          |

|          |     | Software                                                                                       |            |

|          |     | Figure 2.2:Different Options for Driver Installation                                           |            |

|          | 2.3 | Hardware Installation                                                                          | 14         |

|          | 2.4 | Figure 2.3:The Device Name Listed on Device Mng.                                               |            |

|          | 2.4 | Device Setup & Configuration                                                                   | 16         |

|          |     | Figure 2.4:The Device Manager Dialog Box                                                       |            |

|          |     | Figure 2.5:The "Device(s) Found" Dialog Box                                                    |            |

|          |     | 2.4.2 Configuring the Device                                                                   |            |

|          |     | Figure 2.6:The Device Setting Dialog Box                                                       |            |

|          |     | Figure 2.7:The Device Name Appearing on the List of                                            | f          |

|          |     | Devices Box                                                                                    |            |

|          |     | Figure 2.8: The Test Diagram Box for Digital Input                                             |            |

|          |     | Figure 2.9:The Test Diagram Box for Digital Output                                             |            |

| Chapter  | 3   | Pin Assignments & Jumper Settings                                                              |            |

|          | 3.1 | Pin Assignments                                                                                | 22         |

|          |     | Figure 3.1:Connector                                                                           |            |

|          |     | Figure 3.2:I/O Conn.Pin Assig. for PCI-1758UDI                                                 |            |

|          |     | Figure 3.3:I/O Conn. Pin Assig. for PCI-1758UDO                                                |            |

|          |     | Figure 3.4:I/O Conn. Pin Assig. for PCI-1758UDIO . Table 3.1:PCI-1758UDI I/O Conn. Signal Desc |            |

|          |     | Table 3.2:PCI-1/58UDO I/O Connector Signal Desc.                                               | . 20<br>27 |

|          |     | Table 3.3:PCI-1758UDIO I/O Conn. Signal Desc                                                   | . 28       |

|          | 3.2 | Location of Jumpers and DIP Switch                                                             | 29         |

|          |     | Figure 3.5:Location of DIP Switch on PCI-1758UDI                                               |            |

|          |     | Figure 3.6:Location of DIP Switch and Jumper on PC                                             |            |

|          |     | 1758UDO                                                                                        |            |

|          |     | Figure 3.7:Location of DIP Switch and Jumper on PC                                             |            |

|          |     | 1758UDIO                                                                                       | . 30       |

|          | 3.3 | Isolated Digital Input Connections                                      | 30     |

|----------|-----|-------------------------------------------------------------------------|--------|

|          |     | 3.3.1 Interrupt Function of the DI Signals                              |        |

|          |     | 3.3.2 Isolated Inputs                                                   |        |

|          |     | Figure 3.8:Isolated Digital Input Connection                            |        |

|          | 3.4 | Isolated Digital Output Connections                                     | 31     |

|          |     | 3.4.1 Power On Configuration                                            | 32     |

|          |     | Table 3.4:JP1: Power On Config. after Hot Reset  3.4.2 Isolated Outputs | 32     |

|          |     | Figure 3.9:Isolated Digital Output Connection                           |        |

|          | 3.5 | Field Wiring Considerations                                             |        |

|          | 3.6 | Setting the BoardID Switch (SW1)                                        | 34     |

| Chapter  | 4   | Operation                                                               |        |

| -        | 4.1 | Interrupt Function (PCI-1758UDI/UDIO)                                   |        |

|          |     | 4.1.1 IRQ Level                                                         | 36     |

|          |     | 4.1.2 Interrupt Modes for Digital Input                                 | 36     |

|          |     | Figure 4.1:Interrupt Mode for Digital Input                             | 36     |

|          | 4.2 | Digital Filter Function (PCI-1758UDI/UDIO)                              |        |

|          |     | Table 4.1:Pulse Width Filtering                                         | 37     |

|          |     | 4.2.1 Digital Filtering Example                                         | 38     |

|          |     | Figure 4.2:Digital Filter Example                                       |        |

|          |     | 4.2.2 Digital Filter Function Control Register                          | 38     |

|          | 4.3 | Watchdog Timer Function (PCI-1758UDO/UDIO)                              | 39     |

|          | 4.4 | Power-Up States Function (PCI-1758UDO/UDIO)                             |        |

|          | 4.5 | BoardID                                                                 | 40     |

|          |     | Table 4.2:BoardID Reg. of PCI-1758UDI/1758UD                            | O . 40 |

| . 1.     |     | Table 4.3:BoardID Setting (SW1)                                         |        |

| Appendix | A   | Specifications                                                          |        |

|          | A.1 | PCI-1758UDI                                                             |        |

|          | A.2 | PCI-1758UDO                                                             |        |

|          | A.3 | PCI-1758UDIO                                                            |        |

|          | A.4 | General                                                                 |        |

| Appendix | K B | Block Diagram                                                           | 46     |

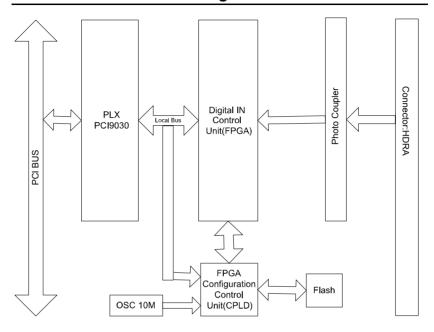

|          | B.1 | PCI-1758UDI Block Diagram                                               | 46     |

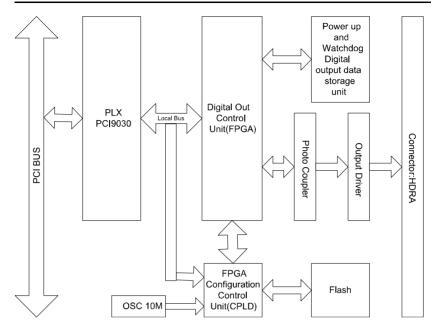

|          | B.2 | PCI-1758UDO Block Diagram                                               | 47     |

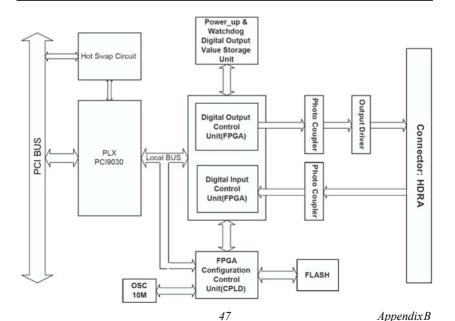

|          | B.3 | PCI-1758UDIO Block Diagram                                              |        |

| Appendix | K C | Register Structure & Format                                             |        |

|          | C.1 | Register Structure                                                      | 50     |

|          | C.2 | PCĬ-1758UDI Register Format                                             | 50     |

|          |     | C.2.1 Register Format                                                   |        |

|          |     | C.2.2 Digital Input Register                                            |        |

|          |     | C.2.3 Digital Input Rising Edge Interrupt Register                      |        |

|          |     | C.2.4 Digital Input Falling Edge Interrupt Register                     |        |

|          |     | C.2.5 Interrupt State Register                                          |        |

|          |     | C.2.6 Interrupt of Port Identify Register                               |        |

|          |     | C.2.7 Digital Filter Function Control Register                          | 56     |

|     | C.2.8  | Filter Interval Time Preset Register          | 57 |

|-----|--------|-----------------------------------------------|----|

| C.3 | PCI-17 | 758 UDO Register Format                       | 58 |

|     | C.3.1  | Digital Output Register                       |    |

|     | C.3.2  | Watchdog Counter Value Register               | 60 |

|     | C.3.3  | Watchdog State/Control Register               | 60 |

|     | C.3.4  | Watchdog Timer Clear Register                 | 61 |

|     | C.3.5  | EEPROM Control/DO state Register              | 62 |

| C.4 | PCI-17 | 758UDIO Register Format                       | 63 |

|     | C.4.1  | Register Format                               |    |

|     | C.4.2  | Digital input Register                        | 64 |

|     | C.4.3  | Digital Output Register                       | 65 |

|     | C.4.4  | Digital input Ring Edge Interrupt Register    | 66 |

|     | C.4.5  | Digital input Falling Edge Interrupt Register | 66 |

|     | C.4.6  | Interrupt State Register                      | 67 |

|     | C.4.7  | Interrupt Of Port Identify Register           | 68 |

|     | C.4.8  | Digital Filter Enable Register                | 68 |

|     | C.4.9  | Filter Interview Time Preset Register         | 69 |

|     | C.4.10 | Watchdog Counter Value Register               | 70 |

|     | C.4.11 | Watchdog State/Control Register               | 70 |

|     | C.4.12 | Watchdog Time Clear Register                  | 71 |

|     | C.4.13 | EEPROM Control/DO state Register              | 72 |

| C.5 | Board  | ID Register                                   | 73 |

### **General Information**

This chapter gives background information on the cards in the PCI-1758U Series. It then shows how to configure the cards to match your application and prepare them for installation on your system.

Sections include:

- Introduction

- Installation Guide

- Accessories

## **Chapter 1 General Information**

#### 1.1 Introduction

Thank you for buying a PCI-1758U Series digital input/output card. The PCI-1758U cards enable powerful data acquisition (DAS) for the PCI bus. It features a unique circuit design, and complete functions for data acquisition and control.

The PCI-1758U cards provides specific functions for different user requirements:

PCI-1758UDO 128-channel Isolated Digital **Output** card

PCI-1758UDI 128-channel Isolated Digital **Input** Card

PCI-1758UDIO 64-channel Isolated Digital Input and

64-channel Isolated Output Card

The following sections of this chapter will provide further information about features of the DAS cards.

#### 1.1.1 Features

PCI-1758U cards provide the most requested I/O and control functions as seen below:

#### PCI-1758UDO

- 128 isolated digital output channels

- High-voltage isolation on output channels (2,500 V DC)

- Wide output range (5  $\sim$  40 V DC)

- High-sink current for isolated output channels (90 mA max./Channel)

- Current protection for each port

- BoardID Switch

- Output status read-back

- Digital output value retained after hot system reset

- Programmable Power-Up States

- · Watchdog Timer

#### PCI-1758UDI

- 128 isolated digital input channels

- High-voltage isolation for input channels (2,500 VDC)

- Wide input range ( $5 \sim 25 \text{ VDC}$ )

- High ESD Protection (2,000 VDC)

- Digital Filter function

- · BoardID Switch

- Interrupt handling capability

#### PCI-1758UDIO

#### Digital Output

- 64 isolated digital output channels

- High-voltage isolation on output channels (2,500 VDC)

- Wide output range (5  $\sim$  40 VDC)

- High-sink current for isolated output channels (90 mA max./Channel)

- · Current protection for each port

- · Output status read-back

- Digital output value retained after hot system reset

- Programmable Power-Up States

- · Watchdog Timer

#### Digital Input

- 64 isolated digital input channels

- High-voltage isolation for input channels (2,500 VDC)

- Wide input range (5  $\sim$  25 VDC)

- High ESD protection (2,000 VDC)

- Digital Filter function

- Interrupt handling capability

- · Robust isolation

- BoardID switch

#### **Robust Isolation**

PCI-1758U cards feature a robust isolation protection for applications in industrial, lab and machinery automation. The PCI-1758U cards can durably withstand a voltage up to 2,500 VDC, preventing your host system from any incidental harms.

#### Wide Input/Output Range

PCI-1758U cards have a wide range of input voltage and it is suitable for most industrial applications with 12 VDC and 24 VDC input voltage. The PCI-1758U cards also feature a wide output voltage range, suitable for most industrial applications with 12 VDC / 24 VDC output voltage. In the mean time, we are also ready to serve your special needs for specific input/output voltage range.

#### PCI-1758UDI

• Input range: 5~25 VDC

#### PCI-1758UDO

• Output range: 5~40 VDC

#### PCI-1758UDIO

Input range: 5~25 VDC

Output range: 5~40 VDC

#### **BoardID Switch**

PCI-1758U cards have a built-in DIP switch that helps define each card's ID when multiple cards have been installed on the same PC chassis. The BoardID switch is very useful when you are building a system with multiple PCI-1758U cards. With correct BoardID settings, you can easily identify and access each card during hardware configuration and software programming.

#### Programmable Power-Up States Function (PCI-1758UDO/UDIO)

When powering up, the output drives on PCI-1758UDO/UDIO are disabled. All output lines are user-configurable for logic high output and logic low output. User-configurable power-up states are useful for ensuring that the PCI-1758UDO/UDIO powers up in a known state. Power-up states are programmed in the EEPROM through the driver. The default settings are all set to 0. For more details, please refer to Appendix C.

#### **Watchdog Timer Function**

The watchdog timer is a software-configurable feature used to set critical outputs to safe states in the event of a software failure. It will activate if there is a loss of communication between the application and the PCI-1758U card. If the PCI-1758U card does not receive a watchdog clear software command within the interval time specified for the watchdog timer, the outputs go to a user-defined safe state and remain in that state until the watchdog timer is disabled and new values are written by the software.

After the watchdog timer expires, the PCI-1758U card ignores any writes until the watchdog timer is disabled. Users can set the watchdog timer timeout period through WDT register to specify the amount of time that must elapse before the watchdog timer expires. The counter on the watchdog timer is configurable up to  $(2^{32-1})$  x 100 ns (approximately seven minutes) before it expires.

#### **Reset Protection**

If the system has undergone a hot reset (i.e. without turning off the system power), the PCI-1758UDO/UDIO can either retain outputs values of each channel, or return to its default configuration with power up status, depending on its onboard jumper setting. This function protects the system from causing wrong operations during unexpected system resets.

| Table 1.1: PCI-1758U Series Features Comparison |                 |                 |                 |  |  |  |

|-------------------------------------------------|-----------------|-----------------|-----------------|--|--|--|

| PCI BUS Isolated Digital I/O card               | PCI-1758UDIO    | PCI-1758UDO     | PCI-1758UDI     |  |  |  |

| Isolated Digital Input                          | Y (64-ch)       | Y (128-ch)      | -               |  |  |  |

| Isolated Digital Output                         | Y (64-ch)       | -               | Y (128-ch)      |  |  |  |

| BoardID                                         | Υ               | Υ               | Υ               |  |  |  |

| 2500 VDC Isolation                              | Υ               | Υ               | Υ               |  |  |  |

| Wide Input Range                                | Y<br>(5~25 VDC) | -               | Y<br>(5~25 VDC) |  |  |  |

| Wide Output Range                               | Y<br>(5~40 VDC) | Y<br>(5~40 VDC) | -               |  |  |  |

| Keep last status after hot reset                | Y               | Y               | -               |  |  |  |

| High Sink current on IDO channels               | Y<br>(90 mA/ch) | Y<br>(90mA/ch)  | -               |  |  |  |

| Output status read back                         | Υ               | Υ               | -               |  |  |  |

| Interrupt handling                              | Υ               | -               | Υ               |  |  |  |

| ESD protection                                  | Y (2000VDC)     | -               | Y (2000VDC)     |  |  |  |

#### 1.2 Installation Guide

Before you install your PCI-1758U card, please make sure you have the following necessary components:

- PCI-1758UDI, PCI-1758UDO or PCI-1758UDIO isolated digital I/O card

- PCI-1758U Series User Manual

- Driver software: Advantech DLL drivers(included in the companion CD-ROM)

- Wiring cable: 100-pin MINI-SCSI HDRA-E100 cable

- Wiring board: ADAM-39100

- Computer: Personal computer or workstation with a PCI-bus slot (running Windows 98/2000/XP)

After you get the necessary components and maybe some accessories for enhanced operation for your DAS card, you can then begin the installation procedure. Figure 1-1 provides a concise flow chart to give users a broad picture of the software and hardware installation procedure.

Figure 1.1: Installation Flow Chart

#### 1.3 Accessories

Advantech offers a complete set of accessory products to support the PCI-1758UDI / 1758UDO cards. These accessories include:

#### 1.3.1 PCL-101100S-1 Wiring Cable

The PCL-101100S-1 (1m) shielded cable is specially designed for the PCI-1758UDI/UDO card to provide high resistance to noise.

#### 1.3.2 ADAM-39100 Wiring Terminal Board

ADAM-39100 is a 100-pin SCSI wiring terminal module for DIN-rail mounting. This terminal module can be readily connected to Advantech PC-LabCard products and allow easy and reliable access to individual pin connections for the PCI-1758UDI/UDO card.

## Installation

This chapter gives users a package item checklist, proper instructions about unpacking and step-by-step procedures for both driver and card installation.

#### Sections include:

- Unpacking

- Driver Installation

- Hardware Installation

- Device Setup and Configuration

## **Chapter 2 Installation**

#### 2.1 Unpacking

After receiving your PCI-1758U product package, please inspect its contents first. The package should contain the following items:

- PCI-1758UDI, PCI-1758UDO or PCI-1758UDIO card

- Companion CD-ROM (Device Drivers included)

- · User Manual

The PCI-1758U cards harbor certain electronic components vulnerable to electrostatic discharge (ESD). ESD could easily damage the integrated circuits and certain components if preventive measures are not carefully paid attention to.

Before removing the card from the antistatic plastic bag, you should take following precautions to ward off possible ESD damage:

- Touch the metal part of your computer chassis with your hand to discharge static electricity accumulated on your body. Or one can also use a grounding strap.

- Touch the anti-static bag to a metal part of your computer chassis before opening the bag.

- Take hold of the card only by the metal bracket when removing it out of the bag.

After taking out the card, you should first:

Inspect the card for any possible signs of external damage (loose or damaged components, etc.). If the card is visibly damaged, please notify our service department or our local sales representative immediately. Avoid installing a damaged card into your system.

Also pay extra caution to the following aspects to ensure proper installation:

- Avoid physical contact with materials that could hold static electricity such as plastic, vinyl and Styrofoam.

- Whenever you handle the card, grasp it only by its edges. DO NOT TOUCH the exposed metal pins of the connector or the electronic components.

Note

Keep the anti-static bag for future use. You might need the original bag to store the card if you have to remove the card from PC or transport it elsewhere.

#### 2.2 Driver Installation

We recommend you to install the driver before you install the PCI-1758U series card into your system, since this will guarantee a smooth installation process.

The Advantech Device Driver Setup program for the PCI-1758U series card is included on the companion CD-ROM that is shipped with your DA&C card package. Please follow the steps below to install the driver software:

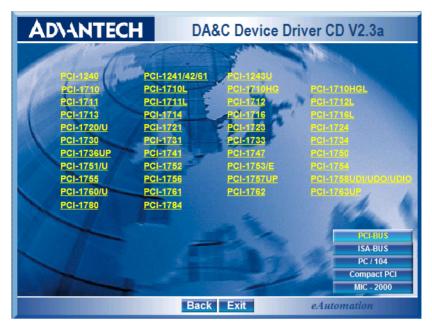

- 1. Insert the companion CD-ROM into your CD-ROM drive.

- 2. The Setup program will be launched automatically if you have the autoplay function enabled on your system. When the Setup Program is launched, you'll see the following Setup Screen.

Note

If the autoplay function is not enabled on your computer, use Windows Explorer or Windows Run command to execute Autorun.exe on the companion CD-ROM.

Figure 2.1: The Setup Screen of Advantech Automation Software

- 3. Select the Individual Drivers option.

- 4. Select the specific device then just follow the installation instructions step by step to complete your device driver installation and setup.

Figure 2.2: Different Options for Driver Installation

For further information on driver-related issues, an online version of the Device Drivers Manual is available by accessing the following path:

Start\Programs\Advantech Automation\Device Manager\Device Driver's Manual

#### 2.3 Hardware Installation

Note Make sure you have installed the driver before you install the card.

(please refer to 2.2 Driver Installation)

After the device driver installation is completed, you can now go on to install the PCI-1758U series card in any PCI slot on your computer. But it is suggested that you refer to the computer user manual or related documentation if you have any doubt. Please follow the steps below to install the card on your system.

- Turn off your computer and unplug the power cord and cables.

TURN OFF your computer before installing or removing any components on the computer.

- 2. Remove the cover of your computer.

- 3. Remove the slot cover on the back panel of your computer.

- 4. Touch the metal part on the surface of your computer to neutralize the static electricity that might be on your body.

- 5. Insert the PCI-1758U series card into a PCI slot. Hold the card only by its edges and carefully align it with the slot. Insert the card firmly into place. Use of excessive force must be avoided, otherwise the card might be damaged.

- 6. Fasten the bracket of the PCI card on the back panel rail of the computer with screws.

- 7. Connect appropriate accessories to the PCI card.

- 8. Replace the cover of your computer chassis. Re-connect the cables you removed in step 2.

- 9. Plug in the power cord and turn on the computer.

Note In case you installed the card without installing the Device Drivers first.

Windows 98/2000/XP will recognize your card as an "unknown device" after rebooting, and will prompt you to provide the necessary driver. You should ignore the prompting messages (just click the Cancel button) and set up the driver according to the steps described in 2.4 Driver Installation.

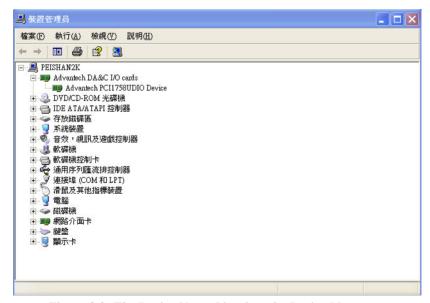

After the PCI-1758U series card is installed, you can verify whether it is properly installed on your system in the Device Manager:

- Access the Device Manager through Control Panel/System/Device Manager.

- 2. The device name of the PCI-1758U series should be listed on the Device Manager tab on the System Property Page.

Figure 2.3: The Device Name Listed on the Device Manager

Note

If your card is properly installed, you should see the device name of your card listed on the Device Manager tab. If you do see your device name listed on it but marked with an exclamation sign "!", it means your card has not been correctly installed. In this case, remove the card device from the Device Manager by selecting its device name and press the Remove button. Then go through the driver installation process again.

After your card is properly installed on your system, you can now configure your device using the Device Installation Program that has itself already been installed on your system during driver setup. Acomplete device installation procedure should include device setup, configuration and testing. The following sections will guide you through the Setup, Configuration and Testing of your device.

### 2.4 Device Setup & Configuration

The Advantech Device Manager program is a utility that allows you to set up, configure and test your device, and later stores your settings on the system registry. These settings will be used when you call the APIs of Advantech Device Drivers.

#### 2.4.1 Setting Up the Device

- 1. To install the I/O device for your card, you must first run the Device Manager program (by accessing Start/Program/Advantech Automation/Device Manager).

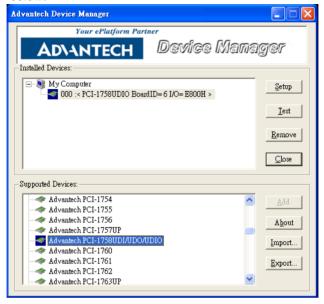

- 2. You can then view the device(s) already installed on your system (if any) on the Installed Devices list box. Since you haven't installed any device yet, you might see a blank list such as the one below (Fig. 2-4).

Figure 2.4: The Device Manager Dialog Box

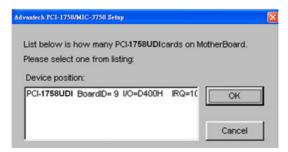

3. Scroll down the *Supported Devices* box to find the device that you wish to install, then click the *Add* button to evoke the existing unconfigured PCI-1758U series dialog box such as one shown in Figure 2.5. The Existing unconfigured PCI-1758U series dialog box. lists all the installed devices on your system. Select the device you want to configure from the list box and press the OK button. After you have clicked OK, you will see a PCI-1758U series Device Setting dialog box such as the one in Fig. 2-6.

Figure 2.5: The "Device(s) Found" Dialog Box

#### 2.4.2 Configuring the Device

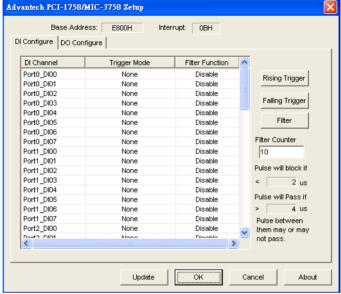

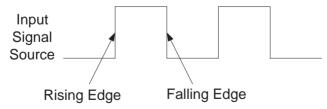

4. On the PCI-1758U series Device Setting dialog box (Fig. 2-6), you can configure the IDI00, IDI01 and DI00, DI01 Interrupt trigger mode either as Rising Edge or Falling Edge, and Enable or Disable the IDI00, IDI01 and DI00, DI01.

Figure 2.6: The Device Setting Dialog Box

5. After you have finished configuring the device, click OK and the device name will appear in the Installed Devices box as seen below:

Figure 2.7: The Device Name Appearing on the List of Devices Box

Note:

As we have noted, the device name "000:<PCI-1758UDI BoardID=6 I/O=800H>" begins with a device number "000", which is specifically assigned to each card. The device number is passed to the driver to specify which device you wish to control.

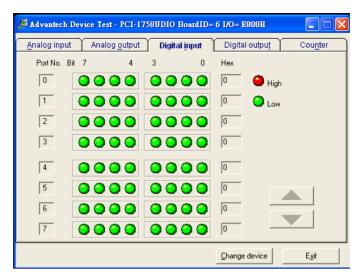

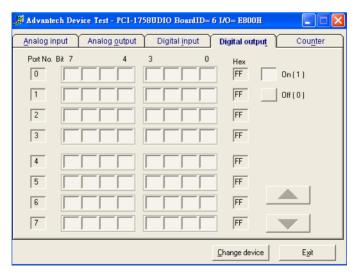

After your card is properly installed and configured, you can click the [**Test...**] button to test your hardware by using the testing utility we supplied. For more detailed information, please refer to Chapter 2 of the Device Drivers Manual.

Figure 2.8: The Test Diagram Box for Digital Input

Figure 2.9: The Test Diagram Box for Digital Output

You can also find examples on the CD-ROM to speed up your programming.

# Pin Assignments and Jumper Settings

Maintaining signal connections is one of the most important factors in ensuring that your application system is sending and receiving data correctly. A good signal connection can avoid unnecessary and costly damage to your system and other hardware devices. This chapter provides useful information about how to connect input and output signals to the PCI-1758U cards via the I/O connector.

#### Sections include:

- Pin Assignments

- Location of Jumper and DIP Switch

- Isolated Digital Input Connections

- Isolated Digital Output Connections

- Field Wiring Considerations

## Chapter 3 Pin Assignments & Jumper Settings

#### 3.1 Pin Assignments

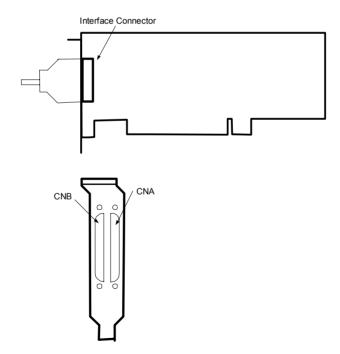

The I/O connector on PCI-1758UDI and PCI-1758UDO is one MINI-SCSI HDRA-E100 Female connector. Figures 3.1, 3.2, 3.3, and 3.4 show the pin assignments for the MINI-SCSI HDRA-E100 Female connector on the PCI-1758UDI and PCI-1758UDO, while Tables 3.1, 3.2, and 3.3 show the connector signal descriptions.

Note: The PCL-101100S-1 (1m) shielded cable is especially designed for the PCI-1758U series to reduce noise in the analog signal lines. Please refer to section 1.3 Accessories.

Figure 3.1: Connector

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CNB                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                                                                              | ΙA                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                   | )                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                          |

| PEF_COMM PEF_COMM PF_IDI07 PF_IDI06 PF_IDI05 PF_IDI01 PF_IDI00 PE_IDI07 PE_IDI00 PE_IDI07 PE_IDI00 PE_IDI07 PE_IDI01 PE_IDI00 PE_IDI00 NC PCD_COMM PCD_COMM PD_IDI07 PD_IDI06 PD_IDI05 PD_IDI04 PD_IDI03 PD_IDI04 PC_IDI07 PC_IDI06 PC_IDI05 PC_IDI07 PC_IDI06 PD_IDI01 PD_IDI00 PC_IDI07 PC_IDI07 PC_IDI06 PD_IDI01 PD_IDI00 PC_IDI07 PC_IDI01 PD_IDI00 PC_IDI07 PC_IDI01 PD_IDI00 PC_IDI07 PC_IDI01 PD_IDI01 PC_IDI01 PC_IDI01 PC_IDI01 PC_IDI01 PC_IDI01 PC_IDI01 PC_IDI01 PC_IDI01 PC_IDI01 NC NC NC NC NC NC NC NC NC | 100 99<br>98 97<br>96 95<br>94 93<br>92 91<br>90 89<br>88 87<br>86 85<br>84 83<br>82 81<br>80 79<br>77 76<br>67 75<br>77 70<br>69 68<br>67 66<br>65 64<br>66 65<br>67 66<br>67 67 57 56<br>67 67 57 56<br>67 57 56<br>67 57 56<br>67 57 57 56<br>67 57 57 57 56<br>67 57 57 57 57 57 57 57 57 57 57 57 57 57 | 50<br>49<br>48<br>47<br>46<br>45<br>44<br>43<br>42<br>41<br>40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32<br>22<br>22<br>21<br>20<br>19<br>11<br>10<br>9<br>8<br>7<br>6<br>5<br>4<br>4<br>3<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 | PAB_COMM PAB_COMM PAB_IDI07 PB_IDI06 PB_IDI05 PB_IDI01 PB_IDI01 PB_IDI01 PB_IDI00 PA_IDI05 PA_IDI05 PA_IDI06 PA_IDI05 PA_IDI01 PA_IDI00 NC P89_COMM P89_COMM P9_IDI07 P9_IDI06 P9_IDI07 P9_IDI06 P9_IDI07 P9_IDI07 P9_IDI07 P9_IDI00 P8_IDI07 P8_IDI007 P | NC N | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 5 16 17 18 19 20 1 22 23 24 22 5 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 | 51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78<br>80<br>81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>94<br>95<br>96<br>97<br>98<br>98<br>99<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90 | NC NC NC NC NC NC NC NC NC P4_IDI00 P4_IDI01 P4_IDI03 P4_IDI05 P4_IDI05 P4_IDI06 P4_IDI07 P5_IDI00 P5_IDI01 P5_IDI02 P5_IDI06 P5_IDI07 P5_IDI06 P5_IDI07 P45_COMM NC |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | `                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\overline{}$                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          | _                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                          |

Figure 3.2: I/O Connector Pin Assignment for PCI-1758UDI

|                      |           | CNB      |                      |                      |          | CNA      |                      |

|----------------------|-----------|----------|----------------------|----------------------|----------|----------|----------------------|

|                      |           |          |                      |                      |          |          |                      |

| 1                    |           |          |                      |                      |          |          |                      |

| PEF_COMP             | 100<br>99 | 50       | PAB_COMP             | P01_COMM             | 1 2      | 51       | P45_COMM             |

| PEF_COMP<br>PF IDO07 | 98        | 49<br>48 | PAB_COMP<br>PB IDO07 | P01_COMM<br>P01_COMM | 3        | 52<br>53 | P45_COMM<br>P45_COMM |

| PF IDO06             | 97        | 47       | PB_IDO07             | P01_COMM             | 4        | 54       | P45_COMM             |

| PF IDO05             | 96        | 46       | PB IDO05             | P01 COMM             | 5        | 55       | P45_COMM             |

| PF_IDO04             | 95        | 45       | PB IDO04             | P01 COMM             | 6        | 56       | P45 COMM             |

| PF IDO03             | 94        | 44       | PB IDO03             | P0 ID000             | 7        | 57       | P4_ID000             |

| PF_IDO02             | 93        | 43       | PB_IDO02             | P0_ID001             | 8        | 58       | P4_ID001             |

| PF_IDO01             | 92        | 42       | PB_IDO01             | P0_ID002             | 9        | 59       | P4_ID002             |

| PF_IDO00             | 91        | 41       | PB_IDO00             | P0_ID003             | 10       | 60       | P4_ID003             |

| PE_IDO07             | 90        | 40       | PA_IDO07             | P0_ID004             | 11       | 61       | P4_ID004             |

| PE_IDO06             | 89        | 39       | PA_IDO06             | P0_ID005             | 12       | 62       | P4_ID005             |

| PE_IDO05             | 88        | 38       | PA_IDO05             | P0_ID006             | 13       | 63       | P4_ID006             |

| PE_IDO04             | 87        | 37       | PA_IDO04             | P0_ID007             | 14       | 64       | P4_ID007             |

| PE_IDO03             | 86        | 36       | PA_IDO03             | P1_ID000             | 15       | 65       | P5_ID000             |

| PE_IDO02             | 85        | 35       | PA_IDO02             | P1_ID001             | 16       | 66       | P5_ID001             |

| PE_IDO01             | 84        | 34       | PA_IDO01             | P1_ID002             | 17       | 67       | P5_ID002             |

| PE_IDO00<br>PEF COMM | 83<br>82  | 33<br>32 | PA_IDO00<br>PAB COMM | P1_ID003<br>P1 ID004 | 18<br>19 | 68       | P5_ID003             |

| PEF_COMM             | 81        | 31       | PAB_COMM<br>PAB COMM | P1_1D004<br>P1 ID005 | 20       | 69<br>70 | P5_ID004<br>P5_ID005 |

| PEF COMM             | 80        | 30       | PAB_COMM             | P1 ID006             | 21       | 71       | P5_ID006             |

| PEF COMM             | 79        | 29       | PAB COMM             | P1 ID007             | 22       | 72       | P5 ID007             |

| PEF COMM             | 78        | 28       | PAB COMM             | P01 COMP             | 23       | 73       | P45 COMP             |

| PEF COMM             | 77        | 27       | PAB COMM             | P01 COMP             | 24       | 74       | P45 COMP             |

| NC                   | 76        | 26       | NC                   | NC                   | 25       | 75       | NC                   |

| NC                   | 75        | 25       | NC                   | NC                   | 26       | 76       | NC                   |

| PCD_COMP             | 74        | 24       | P89_COMP             | P23_COMM             | 27       | 77       | P67_COMM             |

| PCD_COMP             | 73        | 23       | P89_COMP             | P23_COMM             | 28       | 78       | P67_COMM             |

| PD_IDO07             | 72        | 22       | P9_ID007             | P23_COMM             | 29       | 79       | P67_COMM             |

| PD_IDO06             | 71        | 21       | P9_ID006             | P23_COMM             | 30       | 80       | P67_COMM             |

| PD_IDO05             | 70        | 20       | P9_ID005             | P23_COMM             | 31       | 81       | P67_COMM             |

| PD_IDO04             | 69        | 19       | P9_ID004             | P23_COMM             | 32       | 82       | P67_COMM             |

| PD_ID003             | 68<br>67  | 18       | P9_ID003             | P2_ID000             | 33       | 83       | P6_ID000             |

| PD_IDO02<br>PD IDO01 | 66        | 17<br>16 | P9_ID002<br>P9_ID001 | P2_ID001<br>P2_ID002 | 34<br>35 | 84<br>85 | P6_ID001<br>P6 ID002 |

| PD_1D001             | 65        | 15       | P9_ID001<br>P9_ID000 | P2_ID002<br>P2_ID003 | 36       | 86       | P6_ID002<br>P6_ID003 |

| PC_IDO07             | 64        | 14       | P8 ID007             | P2 ID004             | 37       | 87       | P6 ID004             |

| PC IDO06             | 63        | 13       | P8 ID006             | P2 ID005             | 38       | 88       | P6 ID005             |

| PC_IDO05             | 62        | 12       | P8 ID005             | P2 ID006             | 39       | 89       | P6_ID006             |

| PC_IDO04             | 61        | 11       | P8 IDO04             | P2 ID007             | 40       | 90       | P6 ID007             |

| PC IDO03             | 60        | 10       | P8 ID003             | P3 ID000             | 41       | 91       | P7 ID000             |

| PC_IDO02             | 59        | 9        | P8_ID002             | P3_ID001             | 42       | 92       | P7_ID001             |

| PC_IDO01             | 58        | 8        | P8_ID001             | P3_ID002             | 43       | 93       | P7_ID002             |

| PC_IDO00             | 57        | 7        | P8_ID000             | P3_ID003             | 44       | 94       | P7_ID003             |

| PCD_COMM             | 56        | 6        | P89_COMM             | P3_ID004             | 45       | 95       | P7_ID004             |

| PCD_COMM             | 55        | 5        | P89_COMM             | P3_ID005             | 46       | 96       | P7_ID005             |

| PCD_COMM             | 54        | 4        | P89_COMM             | P3_ID006             | 47       | 97       | P7_ID006             |

| PCD_COMM             | 53        | 3        | P89_COMM             | P3_ID007             | 48       | 98       | P7_ID007             |

| PCD_COMM             | 52<br>51  | 2        | P89_COMM             | P23_COMP             | 49       | 99       | P67_COMP             |

| PCD_COMM             | 51        | 1        | P89_COMM             | P23_COMP             | 50       | 100      | P67_COMP             |

|                      |           |          |                      |                      |          |          |                      |

|                      | \         | \ /      |                      |                      |          |          |                      |

|                      |           |          |                      |                      | _        | _        |                      |

Figure 3.3: I/O Connector Pin Assignment for PCI-1758UDO

|           | (        | CNB |           |           | c        | :NA |           |

|-----------|----------|-----|-----------|-----------|----------|-----|-----------|

|           |          |     |           |           |          |     |           |

|           |          |     |           |           |          |     |           |

|           |          |     |           |           |          |     |           |

| P67_COMP  | 100      | 50  | P23_COMP  | NC        | 1        | 51  | NC        |

| P67_COMP  | 99       | 49  | P 23_COMP | NC        | 2        | 52  | NC        |

| P7_IDO07  | 98       | 48  | P3_IDO07  | NC NC     | 3        | 53  | NC        |

| P7 IDO06  | 97       | 47  | P3 IDO06  | NC NC     | 4        | 54  | NC        |

| P7_IDO05  | 96       | 46  | P3_IDO05  | NC        | 5        | 55  | NC        |

| P7 IDO04  | 95       | 45  | P3 IDO04  | NC NC     | 6        | 56  | NC        |

| P7_IDO03  | 94       | 44  | P3 IDO03  | P 0_IDI00 | 7        | 57  | P4_IDI00  |

| P7_IDO02  | 93       | 43  | P3_IDO02  | P0_IDI01  | 8        | 58  | P 4_IDI01 |

| P7_IDO01  | 92       | 42  | P3_IDO01  | P 0_IDI02 | 9        | 59  | P 4_IDI02 |

| P7_IDO00  | 91       | 41  | P3_IDO00  | PO_IDI03  | 10       | 60  | P 4_IDI03 |

| P6_IDO07  | 90       | 40  | P2_IDO07  | P 0_IDI04 | 11       | 61  | P 4_IDI04 |

| P6_IDO06  | 89       | 39  | P2_IDO06  | P 0_IDI05 | 12       | 62  | P 4_IDI05 |

| P6_IDO05  | 88       | 38  | P2_IDO05  | P 0_IDI06 | 13       | 63  | P 4_IDI06 |

| P6_IDO04  | 87       | 37  | P2_IDO04  | P0_IDI07  | 14       | 64  | P4_IDI07  |

| P6_IDO03  | 86       | 36  | P2_IDO03  | P1_IDI00  | 15       | 65  | P5_IDI00  |

| P6_IDO02  | 85       | 35  | P2_IDO02  | P1_IDI01  | 16       | 66  | P.5_IDI01 |

| P6_IDO01  | 84       | 34  | P2_IDO01  | P1_IDI02  | 17       | 67  | P5_IDI02  |

| P6_IDO00  | 83       | 33  | P2_IDO00  | P1_IDI03  | 18       | 68  | P.5_IDI03 |

| P67_COMM  | 82       | 32  | P23_COMM  | P1_IDI04  | 19       | 69  | P5_IDI04  |

| P67_COMM  | 81       | 31  | P23_COMM  | P1_IDI05  | 20       | 70  | P5_IDI05  |

| P67_COMM  | 80       | 30  | P23_COMM  | P1_IDI06  | 21       | 71  | P5_IDI06  |

| P67_COMM  | 79       | 29  | P23_COMM  | P1_IDI07  | 22       | 72  | P5_IDI07  |

| P67_COMM  | 78       | 28  | P23_COMM  | P01_COM   | 23       | 73  | P45_COM   |

| P67_COMM  | 77       | 27  | P23_COMM  | P01_COM   | 24       | 74  | P45_COM   |

| NC        | 76       | 26  | NC        | NC        | 25       | 75  | NC        |

| NC        | 75       | 25  | NC        | NC        | 26       | 76  | NC        |

| P45_COMP  | 74       | 24  | P01_COMP  | NC        | 27       | 77  | NC        |

| P45_COMP  | 73       | 23  | P01_COMP  | NC        | 28       | 78  | NC        |

| P5_IDO07  | 72       | 22  | P1_IDO07  | NC        | 29       | 79  | NC        |

| P5_IDO06  | 71       | 21  | P1_IDO06  | NC        | 30       | 80  | NC        |

| P5_IDO05  | 70       | 20  | P1_IDO05  | NC        | 31       | 81  | NC        |

| P5_IDO04  | 69       | 19  | P1_IDO04  | NC        | 32       | 82  | NC        |

| P5_IDO03  | 68       | 18  | P1_IDO03  | P2_IDI00  | 33       | 83  | P6_IDI00  |

| P5_IDO02  | 67       | 17  | P1_IDO02  | P 2_IDI01 | 34       | 84  | P6_IDI01  |

| P5_IDO01  | 66       | 16  | P1_IDO01  | P 2_IDI02 | 35       | 85  | P6_IDI02  |

| P5_IDO00  | 65       | 15  | P1_IDO00  | P2_IDI03  | 36       | 86  | P6_IDI03  |

| P4_IDO07  | 64       | 14  | P0_IDO07  | P 2_IDI04 | 37       | 87  | P6_IDI04  |

| P4_IDO06  | 63       | 13  | P0_IDO06  | P 2_IDI05 | 38       | 88  | P6_IDI05  |

| P4_IDO05  | 62       | 12  | P0_IDO05  | P2_IDI06  | 39       | 89  | P6_IDI06  |

| P4_IDO04  | 61       | 11  | P0_IDO04  | P 2_IDI07 | 40       | 90  | P6_IDI07  |

| P4_IDO03  | 60       | 10  | P0_IDO03  | P3_IDI00  | 41       | 91  | P7_IDI00  |

| P4_IDO02  | 59       | 9   | P0_IDO02  | P3_IDI01  | 42       | 92  | P7_IDI01  |

| P4_IDO01  | 58       | 8   | P0_IDO01  | P3_IDI02  | 43       | 93  | P7_IDI02  |

| P4_IDO00  | 57       | 7   | PO_IDO00  | P3_IDI03  | 44       | 94  | P7_IDI03  |

| P45_COMM  | 56       | 6   | P01_COMM  | P3_IDI04  | 45       | 95  | P7_IDI04  |

| P45_COMM  | 55<br>54 | 5   | P01_COMM  | P3_IDI05  | 46       | 96  | P.7_IDI05 |

| P 45_COMM | 54       | 4   | P01_COMM  | P3_IDI06  | 47       | 97  | P7_IDI06  |

| P45_COMM  | 53<br>52 | 3   | P01_COMM  | P3_IDI07  | 48       | 98  | P7_IDI07  |

| P45_COMM  | 52<br>51 | 2   | P01_COMM  | P 23_COM  | 49<br>50 | 99  | P67_COM   |

| P45_COMM  | [ "      | '   | P01_COMM  | P23_COM   | 30       | 100 | P67_COM   |

|           |          |     |           |           |          |     |           |

|           |          | )   |           |           |          |     |           |

|           |          |     |           |           | _        |     |           |

Figure 3.4: I/O Connector Pin Assignment for PCI-1758UDIO

| Table 3.1: PCI- | .1758UDI I/O ( | Connector S | ignal Description                |

|-----------------|----------------|-------------|----------------------------------|

| Signal Name     | Reference      | Direction   | Description                      |

| P0_IDI00~ 07    | P01_COMM       | Input       | Isolated Digital Input of port 0 |

| P1_IDI00~ 07    | P01_COMM       | Input       | Isolated Digital Input of port 1 |

| P2_IDI00~ 07    | P23_COMM       | Input       | Isolated Digital Input of port 2 |

| P3_IDI00~ 07    | P23_COMM       | Input       | Isolated Digital Input of port 3 |

| P4_IDI00~ 07    | P45_COMM       | Input       | Isolated Digital Input of port 4 |

| P5_IDI00~ 07    | P45_COMM       | Input       | Isolated Digital Input of port 5 |

| P6_IDI00~ 07    | P67_COMM       | Input       | Isolated Digital Input of port 6 |

| P7_IDI00~ 07    | P67_COMM       | Input       | Isolated Digital Input of port 7 |

| P8_IDI00~ 07    | P89_COMM       | Input       | Isolated Digital Input of port 8 |

| P9_IDI00~ 07    | P89_COMM       | Input       | Isolated Digital Input of port 9 |

| PA_IDI00~ 07    | PAB_COMM       | Input       | Isolated Digital Input of port A |

| PB_IDI00~ 07    | PAB_COMM       | Input       | Isolated Digital Input of port B |

| PC_IDI00~ 07    | PCD_COMM       | Input       | Isolated Digital Input of port C |

| PD_IDI00~ 07    | PCD_COMM       | Input       | Isolated Digital Input of port D |

| PE_IDI00~ 07    | PEF_COMM       | Input       | Isolated Digital Input of port E |

| PF_IDI00~ 07    | PEF_COMM       | Input       | Isolated Digital Input of port F |

| P01_COMM        | -              |             | Common port of port 0 and port 1 |

| P23_COMM        | -              |             | Common port of port 2 and port 3 |

| P45_COMM        | -              |             | Common port of port 4 and port 5 |

| P67_COMM        | -              |             | Common port of port 6 and port 7 |

| P89_COMM        | -              |             | Common port of port 8 and port 9 |

| PAB_COMM        | -              |             | Common port of port A and port B |

| PCD_COMM        | -              |             | Common port of port C and port D |

| PEF_COMM        | -              |             | Common port of port E and port F |

| NC              | -              |             | Not Used                         |

| Table 3.2: PCI | -1758UDO I/O | Connector | Signal Description                |

|----------------|--------------|-----------|-----------------------------------|

| Signal Name    | Reference    | Direction | Description                       |

| P0_IDO00~ 07   | P01_COMM     | Output    | Isolated Digital Output of port 0 |

| P1_IDO00~ 07   | P01_COMM     | Output    | Isolated Digital Output of port 1 |

| P2_IDO00~ 07   | P23_COMM     | Output    | Isolated Digital Output of port 2 |

| P3_IDO00~ 07   | P23_COMM     | Output    | Isolated Digital Output of port 3 |

| P4_IDO00~ 07   | P45_COMM     | Output    | Isolated Digital Output of port 4 |

| P5_IDO00~ 07   | P45_COMM     | Output    | Isolated Digital Output of port 5 |

| P6_IDO00~ 07   | P67_COMM     | Output    | Isolated Digital Output of port 6 |

| P7_IDO00~ 07   | P67_COMM     | Output    | Isolated Digital Output of port 7 |

| P8_IDO00~ 07   | P89_COMM     | Output    | Isolated Digital Output of port 8 |

| P9_IDO00~ 07   | P89_COMM     | Output    | Isolated Digital Output of port 9 |

| PA_IDO00~ 07   | PAB_COMM     | Output    | Isolated Digital Output of port A |

| PB_IDO00~ 07   | PAB_COMM     | Output    | Isolated Digital Output of port B |

| PC_IDO00~ 07   | PCD_COMM     | Output    | Isolated Digital Output of port C |

| PD_IDO00~ 07   | PCD_COMM     | Output    | Isolated Digital Output of port D |

| PE_IDO00~ 07   | PEF_COMM     | Output    | Isolated Digital Output of port E |

| PF_IDO00~ 07   | PEF_COMM     | Output    | Isolated Digital Output of port F |

| P01_COMM       | -            |           | Negative external power supply    |

| P23_COMM       | -            |           | Negative external power supply    |

| P45_COMM       | -            |           | Negative external power supply    |

| P67_COMM       | -            |           | Negative external power supply    |

| P89_COMM       | -            |           | Negative external power supply    |

| PAB_COMM       | -            |           | Negative external power supply    |

| PCD_COMM       | -            |           | Negative external power supply    |

| PEF_COMM       | -            |           | Negative external power supply    |

| P01_COMP       | -            |           | Positive external power supply    |

| P23_COMP       | -            |           | Positive external power supply    |

| P45_COMP       | -            |           | Positive external power supply    |

| P67_COMP       | -            |           | Positive external power supply    |

| P89_COMP       | -            |           | Positive external power supply    |

| PAB_COMP       | -            |           | Positive external power supply    |

| PCD_COMM       | -            |           | Positive external power supply    |

| PEF_COMM       | -            |           | Positive external power supply    |

| NC             | -            | -         | Not used                          |

| Table 3.3: PC | I-1758UDIC | O I/O Conn | ector Signal Description                       |

|---------------|------------|------------|------------------------------------------------|

| Signal Name   | Reference  | Direction  | Description                                    |

| P0_IDI00~ 07  | DI COM0    | Input      | Isolated Digital Input of port 0               |

| P1_IDI00~ 07  | DI COM1    | Input      | Isolated Digital Input of port 1               |

| P2_IDI00~ 07  | DI COM2    | Input      | Isolated Digital Input of port 2               |

| P3_IDI00~ 07  | DI COM3    | Input      | Isolated Digital Input of port 3               |

| P4_IDI00~ 07  | DI COM4    | Input      | Isolated Digital Input of port 4               |

| P5_IDI00~ 07  | DI COM5    | Input      | Isolated Digital Input of port 5               |

| P6_IDI00~ 07  | DI COM6    | Input      | Isolated Digital Input of port 6               |

| P7_IDI00~ 07  | DI COM7    | Input      | Isolated Digital Input of port 7               |

| P01_COM       | -          |            | Common port of Digital Input port 0 and port 1 |

| P23_COM       | -          |            | Common port of Digital Input port 0 and port 1 |

| P45_COM       | -          |            | Common port of Digital Input port 0 and port 1 |

| P67_COM       | -          |            | Common port of Digital Input port 0 and port 1 |

| P0_IDO00~ 07  | СОМ0       | Output     | Isolated Digital Output of port 0              |

| P1_IDO00~ 07  | COM1       | Output     | Isolated Digital Output of port 1              |

| P2_IDO00~ 07  | COM2       | Output     | Isolated Digital Output of port 2              |

| P3_IDO00~ 07  | COM3       | Output     | Isolated Digital Output of port 3              |

| P4_IDO00~ 07  | COM4       | Output     | Isolated Digital Output of port 4              |

| P5_IDO00~ 07  | COM5       | Output     | Isolated Digital Output of port 5              |

| P6_IDO00~ 07  | COM6       | Output     | Isolated Digital Output of port 6              |

| P7_IDO00~ 07  | COM7       | Output     | Isolated Digital Output of port 7              |

| P01_COMM      | -          |            | Negative external power supply                 |

| P23_COMM      | -          |            | Negative external power supply                 |

| P45_COMM      | -          |            | Negative external power supply                 |

| P67_COMM      | -          |            | Negative external power supply                 |

| P01_COMP      | -          |            | Positive external power supply                 |

| P23_COMP      | -          |            | Positive external power supply                 |

| P45_COMP      | -          |            | Positive external power supply                 |

| P67_COMP      | -          |            | Positive external power supply                 |

**Note:** Each PEF\_COMM pin can tolerate no more than 300 mA. Make sure that every PEF\_COMM pin is properly connected to the equipment's ground (GND).

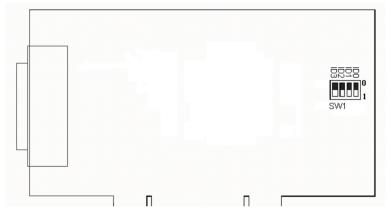

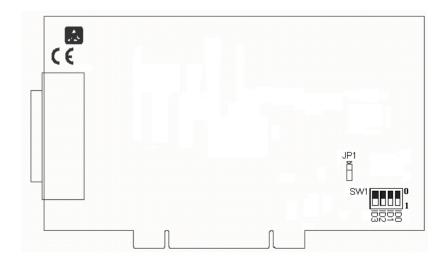

#### 3.2 Location of Jumpers and DIP Switch

Figure 3.5, 3.6, and 3.7 show the names and locations of jumpers and DIP switches on the PCI-1758U cards. There is one DIP switch SW1 on PCI-1758UDI, and there is one DIP switch SW1 and one jumper JP1 on the PCI-1758UDO and PCI-1758UDIO.

Figure 3.5: Location of DIP Switch on PCI-1758UDI

Figure 3.6: Location of DIP Switch and Jumper on PCI-1758UDO

Figure 3.7: Location of DIP Switch and Jumper on PCI-1758UDIO SW1: BoardID setting, JP1: Power on configuration after hot reset

#### 3.3 Isolated Digital Input Connections

#### PCI-1758UDI

PCI-1758UDI has 128 isolated digital input channels designated:

```

P0_IDI00~07, P1_IDI00~07, P2_IDI00~07, P3_IDI00~07, P4_IDI00~07, P5_IDI00~07, P6_IDI00~07, P7_IDI00~07, P8_IDI00~07, P9_IDI00~07, PA_IDI00~07, PB_IDI00~07, PC_IDI00~07, PD_IDI00~07, PE_IDI00~07, PF_IDI00~07

```

#### PCI-1758UDIO

PCI-1758UDIO has 64 isolated digital input channels designated P0\_IDI00~07, P1\_IDI00~07, P2\_IDI00~07, P3\_IDI00~07, P4\_IDI00~07, P5\_IDI00~07, P6\_IDI00~07, P7\_IDI00~07.

#### 3.3.1 Interrupt Function of the DI Signals

All channels in PCI-1758UDI/UDIO can be used to generate hardware interrupts. Setup the configuration of interrupts by programming the interrupt control register. For detailed information, please refer to Section 5.1 Interrupt Function.

#### 3.3.2 Isolated Inputs

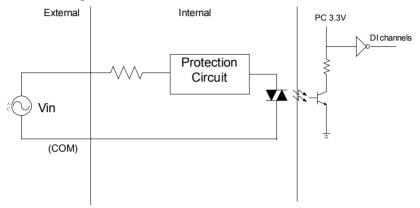

Each of the isolated digital input channels accepts 5~25 VDC voltage inputs (5~30 VDC for PCI-1758UDIO), and also accept bi-directional input. This means that you can apply positive or negative voltage to an isolated input pin. Each group of 16 channels share one common pin. Figure 3.8 shows how to connect an external input source to one of the card's isolated input channels.

Figure 3.8: Isolated Digital Input Connection

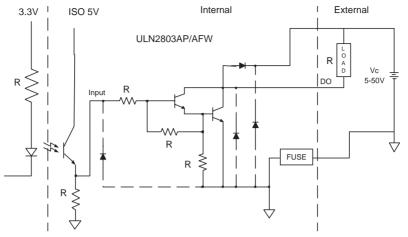

#### 3.4 Isolated Digital Output Connections

#### **PCI-1758UDO**

PCI-1758UDO has 128 isolated digital output channels designated P0\_IDO00~7, P1\_IDO00~7, P2\_IDO00~7, P3\_IDO00~7, P4\_IDO00~7, P5\_IDO00~7, P6\_IDO00~7, P7\_IDO00~7. P8\_IDO00~7, P9\_IDO00~7, PA\_IDO00~7, PB\_IDO00~7, PC\_IDO00~7, PD\_IDO00~7, PE\_IDO00~7, and PF\_IDO00~7.

#### PCI-1758UDIO

PCI-1758UDIO has 64 isolated digital output channels designated P0\_IDO00~7, P1\_IDO00~7, P2\_IDO00~7, P3\_IDO00~7, P4\_IDO00~7, P5\_IDO00~7, P6\_IDO00~7, P7\_IDO00~7.

#### 3.4.1 Power On Configuration

The default configuration will be set after power is turned on. The hardware reset sets all the isolated output channels to "off" status (The current of the load can not be sink mode). So you do not need to worry about damaging external devices during system startup or reset. When the system is hot reset, the status of the isolated digital output channels can be selected by jumper JP1. Table 3.4 shows the configuration of jumper JP1.

| Table 3.4: JP1: Power On Configuration after Hot Reset |                                                     |  |  |

|--------------------------------------------------------|-----------------------------------------------------|--|--|

| JP1 on PCI-<br>1758UDO / UDIO                          | Power on configuration after hot reset              |  |  |

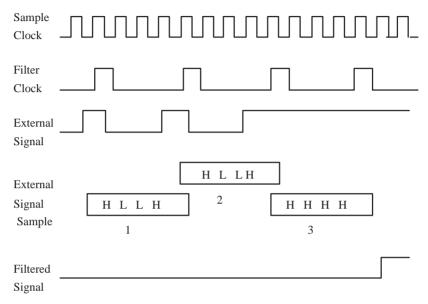

| 1 2 3                                                  | Keep the last digital output status after hot reset |  |  |