# **PCI-1718 Series**

12-bit Multifunction Cards with Universal PCI Bus

**User Manual**

#### Copyright

The documentation and the software included with this product are copyrighted 2005 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

#### Acknowledgements

Intel and Pentium are trademarks of Intel Corporation.

Microsoft Windows and MS-DOS are registered trademarks of Microsoft Corp.

All other product names or trademarks are properties of their respective owners.

This Manual Covers the Following Models

- PCI-1718HDU

- PCI-1718HGU

Part No. 2003171801 Printed in Taiwan 2nd Edition Nov 2005

#### **Product Warranty (2 years)**

Advantech warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by Advantech, or which have been subject to misuse, abuse, accident or improper installation. Advantech assumes no liability under the terms of this warranty as a consequence of such events.

Because of Advantech's high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an Advantech product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- 1. Collect all the information about the problem encountered. (For example, CPU speed, Advantech products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain an RMA (return merchandise authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

#### CE

This product has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### **Technical Support and Assistance**

- Step 1. Visit the Advantech web site at **www.advantech.com/support** where you can find the latest information about the product.

- Step 2. Contact your distributor, sales representative, or Advantech's customer service center for technical support if you need additional assistance. Please have the following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

# **Packing List**

Before setting up the system, check that the items listed below are included and in good condition. If any item does not accord with the table, please contact your dealer immediately.

- PCI-1718HDU/HGU DA&C card

- PCI-1718HDU/HGU User Manual

- Companion CD-ROM with DLL drivers

# **Safety Precaution - Static Electricity**

Follow these simple precautions to protect yourself from harm and the products from damage.

- 1. To avoid electrical shock, always disconnect the power from your PC chassis before you work on it. Don't touch any components on the CPU card or other cards while the PC is on.

- 2. Disconnect power before making any configuration changes. The sudden rush of power as you connect a jumper or install a card may damage sensitive electronic components.

# Contents

| Chapter | 1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2      |

|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| •       | 1.1 | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|         | 1.2 | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4      |

|         | 1.3 | Installation Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5      |

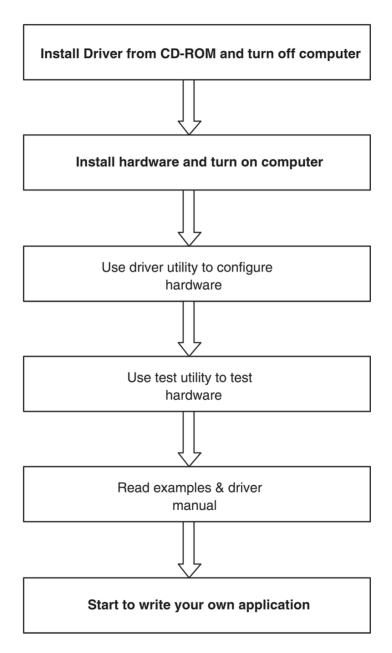

|         |     | Figure 1.1:Installation Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6      |

|         | 1.4 | Software Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7      |

|         | 1.5 | Device Driver Programming Roadmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8      |

|         | 1.6 | Accessories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| Chapter | 2   | Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 12   |

|         | 2.1 | Unpacking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12     |

|         | 2.2 | Driver Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13     |

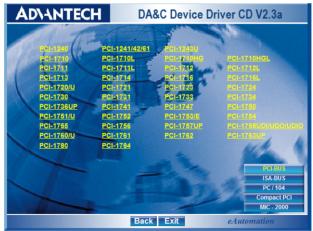

|         |     | Figure 2.1:Setup Screen of Advantech Automation S<br>ware 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | oft-   |

|         |     | Figure 2.2:Different Options for Driver Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

|         | 2.3 | Hardware Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15     |

|         | 2.4 | Device Setup & Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16     |

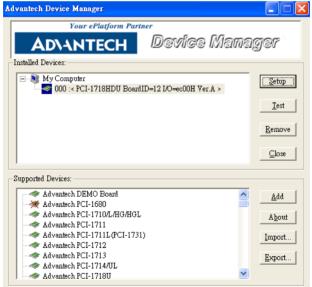

|         |     | Figure 2.3:The Device Manager Dialog Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

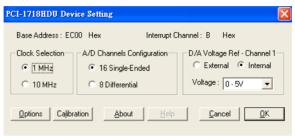

|         |     | Figure 2.4:The Device Setting Dialog Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|         |     | Figure 2.5:Device Name Appearing on the List of Device Name Appearing on the Device Name Appear | evic-  |

|         |     | es Box 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.0    |

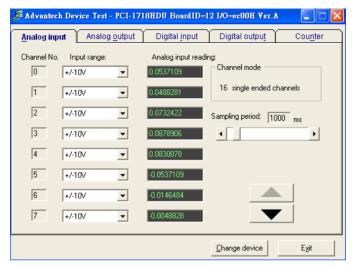

| ~-      | _   | Figure 2.6:The Test Utility Dialog Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| Chapter | 3   | Signal Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

|         | 3.1 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20     |

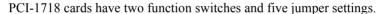

|         | 3.2 | Switch and Jumper Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20     |

|         |     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .10118 |

|         |     | 3.2.1 Setting the BoardID Switch (SW1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21     |

|         |     | Table 3.1:Board ID Setting (SW1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21     |

|         |     | 3.2.2 Channel Configuration, S/E or DIFF (SW2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22     |

|         |     | Table 3.2:Summary of Switch SW2 Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

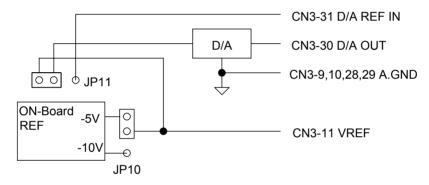

|         |     | 3.2.3 D/A Reference Voltage, int./ext. (JP11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

|         |     | Table 3.3:Summary of Jumper JP11 Settings 3.2.4 Internal Voltage Reference, -10 V or -5 V (JP10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23     |

|         |     | Table 3.4:Summary of Jumper JP10 Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23     |

|         |     | Table 3.5:Summary of Jumper JP8 Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24     |

|         |     | 3.2.6 Ext. trigger and Counter Gate 0 Control (JP5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

|         |     | Table 3.6:Summary of Jumper Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25     |

|         |     | Table 3.7:Summary of Jumper Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

|         |     | 3.2.8 Setting the Time to Reset Digital Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27     |

|         |     | Table 3.8:JP21 Jumper Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

|         | 3.3 | Signal Connections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28     |

|         |     | Figure 3.2:I/O Connector Pin Assignments for the Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CI-    |

#### 1718 Series 28

|                 |                                                      | 3.3.1 I/O Connector Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 29                                                                                                     |

|-----------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                 |                                                      | Table 3.9:I/O Connector Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 29                                                                                                     |

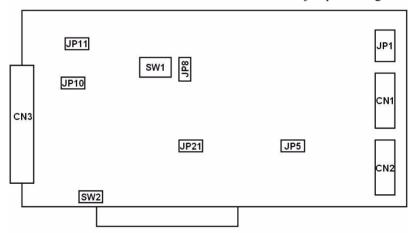

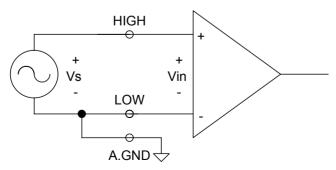

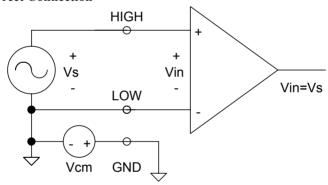

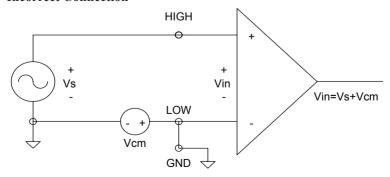

|                 |                                                      | 3.3.2 Analog Input Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 30                                                                                                     |

|                 |                                                      | Figure 3.3: Analog Output Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

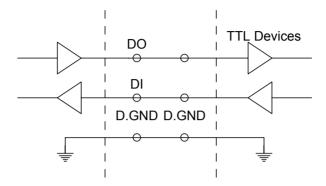

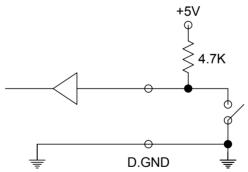

|                 |                                                      | 3.3.3 Digital Signal Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 34                                                                                                     |

|                 | 3.4                                                  | Field Wiring Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35                                                                                                       |

| Chapter         | 4                                                    | Programming Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38                                                                                                       |

| -               | 4.1                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                          |

|                 | 4.2                                                  | Programming with the Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38                                                                                                       |

|                 | 4.3                                                  | Register Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38                                                                                                       |

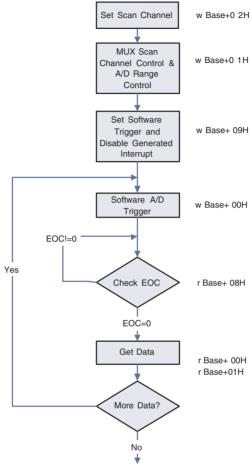

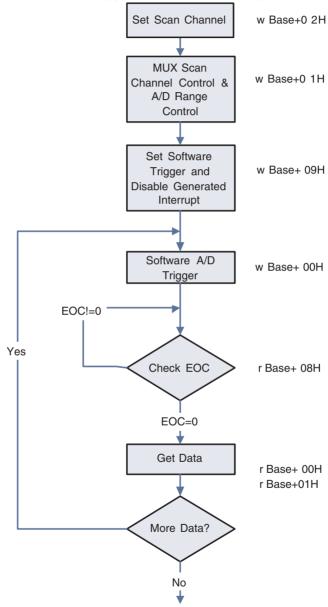

|                 |                                                      | 4.3.1 Software Trigger and Polling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 39                                                                                                     |

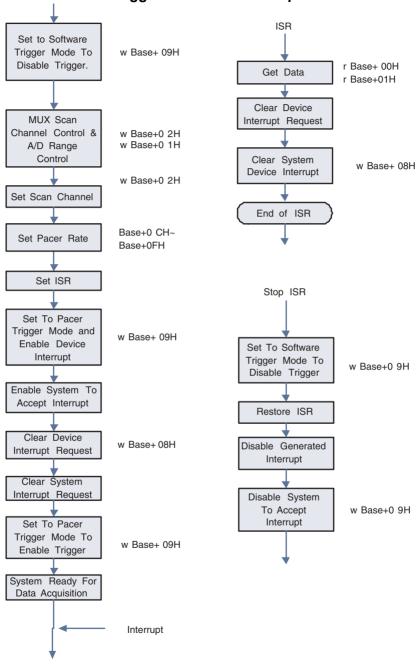

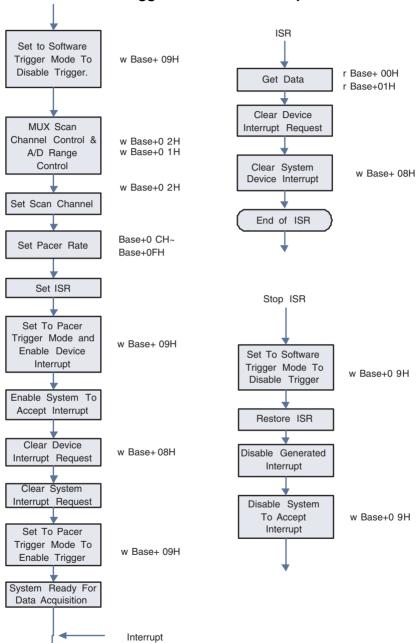

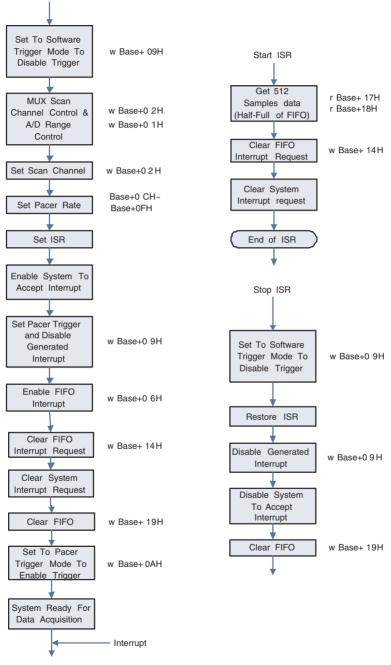

|                 |                                                      | 4.3.2 Pacer Trigger Mode with Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 41                                                                                                     |

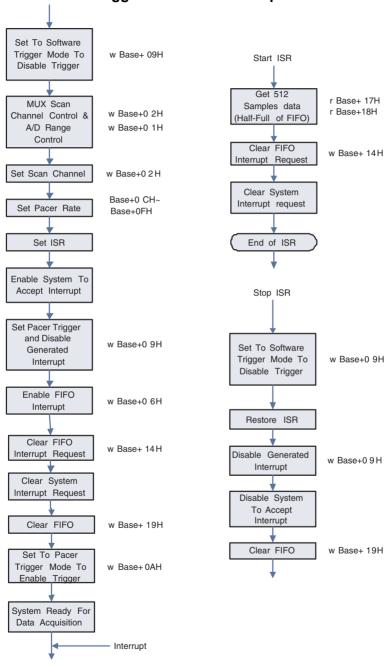

|                 |                                                      | 4.3.3 Pacer Trigger Mode with Interrupt and FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 45                                                                                                     |

|                 | 4.4                                                  | Programming with LabVIEW and ActiveDAQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |

| Appendix        | A                                                    | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>52</b>                                                                                                |

|                 | A.1                                                  | Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52                                                                                                       |

|                 | A.2                                                  | Analog Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                                                                       |

|                 | A.3                                                  | Digital Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                       |

|                 | A.4                                                  | Digital Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                                                                                       |

|                 | A.5                                                  | Counter/Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|                 | A.6                                                  | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56                                                                                                       |

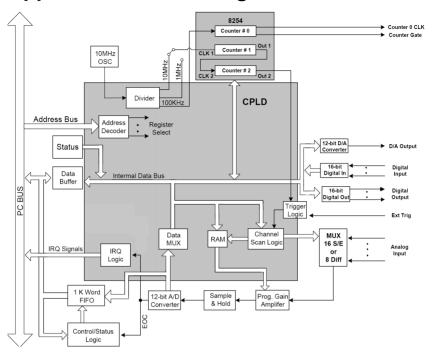

| <b>Appendix</b> | В                                                    | Block Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>58</b>                                                                                                |

| Annandir        | - 0                                                  | D '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                        |

| Appendix        |                                                      | Register Structure & Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                                                                                                       |

| Appendix        |                                                      | Register Structure & Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                          |

| Appendix        | C.1<br>C.2                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                       |

| Appenuix        | C.1                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                       |

| Аррепиіх        | C.1                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60<br>60<br>(1)                                                                                          |

| Аррепціх        | C.1                                                  | Overview I/O Port Address Map Table C.1:PCI-1718HDU/HGU Register Format (Part 61 Table C.2:PCI-1718HDU/HGU Register Format (Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60<br>60<br>(1)                                                                                          |

| Appendix        | C.1                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60 60 1)                                                                                                 |

| Appendix        | C.1                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60<br>60<br>(1)<br>(2)                                                                                   |

| Аррепціх        | C.1<br>C.2                                           | Overview I/O Port Address Map Table C.1:PCI-1718HDU/HGU Register Format (Part 61 Table C.2:PCI-1718HDU/HGU Register Format (Part 62 Table C.3:PCI-1718HDU/HGU Register Format (Part 63 A/D Data and Channels — BASE+00H~01H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60<br>60<br>1)<br>2)<br>3)<br>64                                                                         |

| Аррепціх        | C.1<br>C.2                                           | Overview I/O Port Address Map Table C.1:PCI-1718HDU/HGU Register Format (Part 61 Table C.2:PCI-1718HDU/HGU Register Format (Part 62 Table C.3:PCI-1718HDU/HGU Register Format (Part 63 A/D Data and Channels — BASE+00H~01H Table C.4:Register for A/D Data and Channels Software A/D Trigger — BASE+00H                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60<br>60<br>1)<br>2)<br>3)<br>64<br>64                                                                   |

| Аррепціх        | C.1<br>C.2<br>C.3<br>C.4                             | Overview I/O Port Address Map Table C.1:PCI-1718HDU/HGU Register Format (Part 61 Table C.2:PCI-1718HDU/HGU Register Format (Part 62 Table C.3:PCI-1718HDU/HGU Register Format (Part 63 A/D Data and Channels — BASE+00H~01H Table C.4:Register for A/D Data and Channels Software A/D Trigger — BASE+00H Table C.5:Register for Software A/D Trigger                                                                                                                                                                                                                                                                                                                                                                                         | 60<br>60<br>61<br>61<br>62<br>64<br>64<br>64                                                             |