## PCI-1712/1732 User's manual 1 MS/s, 12-bit, 16-ch High-Speed Multifunction Card

## Unpacking

The PCI-1712/1732 package should contain the following items:

- **PCI-1712/1732** card

- Companion CD-ROM disc

- 🗹 User's Manual

- 🗹 Quick Start

## **Driver Installation**

- Step 1: Insert the companion disc into your CD-ROM drive.

- **Step 2**: The *Setup Program* will be launched automatically, and you'll see the following *Setup Screen*.

Select the *DLL Drivers* installation option. (If *autoplay* is not enabled, please use

Windows Explorer or Windows Run command to execute setup.exe on CD-ROM).

- Step 3: Select the Windows 95/98 or Windows NT option according to your operating system.

- Step 4: Follow the installation instructions step by step to complete your DLL driver setup.

## Hardware Installation

- Step 1: Turn off your computer and unplug the power cord and cables

- Step 2: Remove the cover of your computer

- Step 3: Remove the slot cover on the back panel of your computer

- **Step 4**: Touch the metal part of your computer chassis to discharge static electricity on your body

- **Step 5**: Insert the PCI-1712/1732 card into a PCI slot. Hold the card only by its edges and carefully align it with the slot, then insert the card firmly into place. Use of excessive force must be avoided otherwise the card might be damaged.

- **Step 6**: Fasten the bracket of the PCI card on the back panel rail of the computer with screws

- Step 7: Connect appropriate accessories (68-pin cable, wiring terminals, etc., if necessary) to the PCI card.

- Step 8: Replace the cover of your computer chassis. Re-connect the cables you removed in step 2.

- Step 9:Plug in the power cord and turn on the computer

## Verifying your Installation

• Access the *Device Manager* through the *Control Panel/System/Device Manager*. On the *Device Manager* tab of the *System Property* sheet, you can see the *Device Name* of the PCI-1712/1732 listed on it.

| System Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ? ×  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| General Device Manager Hardware Profiles Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| View devices by type     C View devices by connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Constant     Constant |      |

| Propetties Refresh Remove Print                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| OK Car                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ncel |

## **Device Installation**

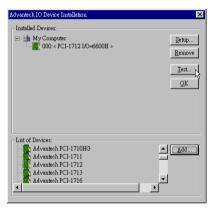

Step 1: Run the Device Installation program (by accessing Start/Programs/ Advantech Driver for 95 and 98 (or for NT)/Device Installation).

Step 2: On the Device Installation program window, select the Device menu item on the menu bar, and click the Setup command to bring up the I/O Device Installation dialog box as below:

| Advantech IO Device Installation                                                                             | X                   |

|--------------------------------------------------------------------------------------------------------------|---------------------|

| Installed Devices:                                                                                           |                     |

| 🔛 My Computer                                                                                                | Setup<br>Remove     |

|                                                                                                              | QK                  |

| List of Devices:                                                                                             |                     |

| Advantech PCI-1710HG<br>Advantech PCI-1711<br>Advantech PCI-1712<br>Advantech PCI-1713<br>Advantech PCI-1713 | <u>Approxectors</u> |

|                                                                                                              |                     |

Step 3: Scroll down the *List of Devices* box to find the device that you wish to configure, then click the *Add* button to bring up the *Device Found(s)* dialog box as shown below:

| Advantech PCI-1712 device(s) found                                 | ×        |

|--------------------------------------------------------------------|----------|

| List below is how many PCI-1712 cards on<br>Please select one from |          |

| Device<br>PCI-1712 Slot= 0 1/0= 6600H IRQ= 1                       |          |

|                                                                    | <u> </u> |

|                                                                    | Cancel   |

|                                                                    |          |

- Step 4: After selecting a device and click OK, the Device Setting dialog box will pop up. You can configure various settings for the selected device.

- **Step 5**: After you have finished configuring of the device, click *OK* and the device will appear in the *Installed Devices* box as seen below:

Step 6: After your card is properly installed and configured, you can click the *Test* button to test your hardware.

| ,왜 Advantech Device Test - 000 : {PCI-1 | 712 I/O=6600H}    |                    |          |

|-----------------------------------------|-------------------|--------------------|----------|

| Analog input Analog output              | Digital input     | Digital output     | Counter  |

| Channel No. Input range:                | Analog input read |                    |          |

| 0 0.10V 💌                               | 0.0000000         | - Channel mode     |          |

| 1 0·10/ 💌                               | 0.0000000         | 16 single ended o  | hannels  |

| 2 0.10V 💌                               | 0.0000000         | Sampling period 10 | 100 mo   |

| 3 0.10v 💌                               | 0.0000000         |                    | •        |

| 4 0.10v 💌                               | 0.0000000         |                    |          |

| 5 0.10V <b>•</b>                        | 0.0000000         |                    |          |

| 6 0.10V ·                               | 0.0000000         |                    | <u> </u> |

| 7 010v 💌                                | 0.0000000         |                    |          |

|                                         |                   | Change device      | Eyi      |

Step 7: You can test your hardware by using the testing utility we supplied. For more detailed information, please refer to Chapter 2 of the User's Manual.

#### **Copyright**°

This documentation and the software included with this product are copyrighted 2000 by Advantech Co., Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice.

No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties which may result from its use.

#### Acknowledgments

PC-LabCard is a trademark of Advantech Co., Ltd. IBM and PC are trademarks of International Business Machines Corporation. MS-DOS, Windows<sup>®</sup>, Microsoft<sup>®</sup> Visual C++ and Visual BASIC are trademarks of Microsoft<sup>®</sup> Corporation. Intel<sup>®</sup> and Pentium<sup>®</sup> are trademarks of Intel Corporation. Delphi and C++Builder are trademarks of Inprise Corporation.

#### **CE notification**

The PCI-1712/1732, developed by ADVANTECH CO., LTD., has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from Advantech. Please contact your local supplier for ordering information.

#### **On-line Technical Support**

For technical support and service, please visit our support website at:

#### http://support.advantech.com

Part No. 2003171200 1st Edition Printed in Taiwan September 2000

# Contents

| 1. | Intro | duction1                        |

|----|-------|---------------------------------|

|    | 1.1   | Features                        |

|    | 1.2   | Installation Guide              |

|    | 1.3   | Accessories                     |

| 2. | Insta | allation                        |

|    | 2.1   | Unpacking7                      |

|    | 2.2   | Driver Installation             |

|    | 2.3   | Hardware Installation           |

|    | 2.4   | Device Setup & Configuration 12 |

|    | 2.5   | Device Testing 15               |

| 3. | Sign  | al Connections 19               |

|    | 3.1   | Overview                        |

|    | 3.2   | I/O Connector                   |

|    | 3.3   | Analog Input Connections        |

|    | 3.4   | Analog Output Connections       |

|    | 3.5   | Field Wiring Considerations     |

| 4. | Soft  | ware Overview 29                |

|    | 4.1   | Programming Choices             |

|    | 4.2   | DLL Driver Programming Roadmap  |

| 5. | Princ | ciples of Operation33           |

|    | 5.1   | Analog Input Features           |

|    | 5.2   | Analog Output Features 40       |

|    | 5.3   | Digital I/O Features            |

|    | 5.4   | Counter/Timer Features          |

| 6. Calik | pration                                           | 55 |

|----------|---------------------------------------------------|----|

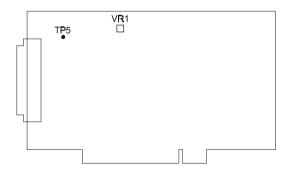

| 6.1      | VR Assignment                                     | 55 |

| 6.2      | A/D Calibration                                   | 56 |

| 6.31     | D/A Calibration                                   | 57 |

| 6.40     | Calibration Utility                               | 58 |

| Appen    | dix A. Specification                              | 69 |

| Appen    | dix B. Block Diagram                              | 73 |

| Appen    | dix C. Screw-terminal Board                       | 75 |

| C.1      | Introduction                                      | 75 |

| C.2      | Features                                          | 75 |

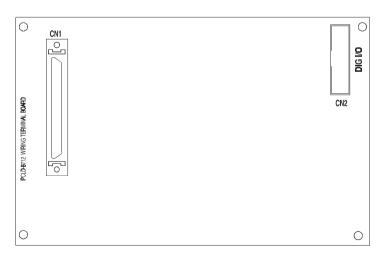

| C.3      | Board Layout                                      |    |

| C.4      | Pin Assignment                                    |    |

| C.5      | Single-ended Connections                          | 77 |

| C.6      | Differential Connections                          | 78 |

| Appen    | dix D. Register Structure and Format              | 79 |

| D.1      | Overview                                          |    |

| D.2      | I/O Port Address Map                              |    |

| D.3      | A/D Single Value Acquisition — Write BASE+0       | 83 |

| D.4      | Channel and A/D data — Read BASE + 0              | 83 |

| D.5      | A/D Channel Range Setting — Write BASE+2          | 84 |

| D.6      | MUX Control — Write BASE+4                        | 85 |

| D.7      | A/D Control/Status Register — Write/Read BASE+6   | 87 |

| D.8      | Clear interrupt and FIFO — Write BASE+8           | 89 |

| D.9      | Interrupt and FIFO status — Read BASE+8           | 90 |

| D.10     | ) D/A control/status register — Write/Read BASE+A | 91 |

| D.11     | D/A Channel 0/1 Data — Write BASE+C/E             | 93 |

| D.12     | 2 82C54 Counter Chip 0 — Write/Read BASE+10 to 16 |    |

| D.13     | 8 82C54 counter chip 1 — Write/Read BASE+18 to 1E | 95 |

| D.14 | Counter gate and clock control/status — Write/ Read BASE+20 |            |

|------|-------------------------------------------------------------|------------|

|      | to 26                                                       | 96         |

| D.15 | Digital I/O registers — Write/Read BASE+28                  | <b>9</b> 9 |

| D.16 | Digital I/O configuration registers — Write/Read BASE+2A 1  | 100        |

| D.17 | Calibration command registers — Write BASE+2C               | 100        |

| D.18 | D/A Channel Data for Continuous Output Operation Mode —     |            |

|      | Write BASE+30                                               | 102        |

# Figures

| Figure 2-1:  | The Setup Screen of Advantech Automation Software        | 8  |

|--------------|----------------------------------------------------------|----|

| Figure 2-2:  | Different options for Driver Setup                       | 9  |

| Figure 2-3:  | The device name listed on the Device Manager             | 11 |

| Figure 2-4:  | The Advantech Device Installation utility program        | 12 |

| Figure 2-5:  | The I/O Device Installation dialog box                   | 12 |

| Figure 2-6:  | The "Device(s) Found" dialog box                         | 13 |

| Figure 2-7:  | The Device Setting dialog box                            | 13 |

| Figure 2-8:  | The Device Name appearing on the list of devices box     | 14 |

| Figure 2-9:  | Analog Input tab on the Device Test dialog box           | 15 |

| Figure 2-10: | Analog Input tab on the Device Test dialog box           | 16 |

| Figure 2-11: | Analog Output tab on the Device Test dialog box          | 16 |

| Figure 2-12: | Digital Input tab on the Device Test dialog box          | 17 |

| Figure 2-13: | Digital Output tab on the Device Test dialog box         | 17 |

| Figure 2-14: | Digital output tab on the Device Test dialog box         | 18 |

| Figure 3-1:  | I/O connector pin assignments for the PCI-1712/1732      | 20 |

| Figure 3-2:  | Single-ended input channel connection                    | 24 |

| Figure 3-3:  | Differential input channel connection - ground reference |    |

|              | signal source                                            | 25 |

| Figure 3-4:  | Differential input channel connection - floating signal  |    |

|              | source                                                   | 26 |

| Figure 3-5:  | Analog output connections                                | 27 |

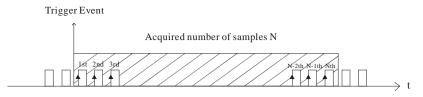

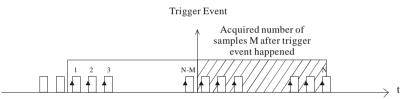

| Figure 5-1:  | Post-Trigger Acquisition Mode                            | 35 |

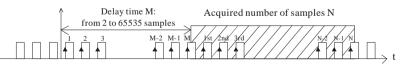

| Figure 5-2:  | Delay-Trigger Acquisition Mode                           | 35 |

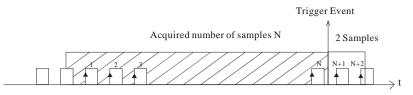

| Figure 5-3:  | About-Trigger Acquisition Mode                           | 36 |

| Figure 5-4:  | Pre-Trigger Acquisition Mode                             | 37 |

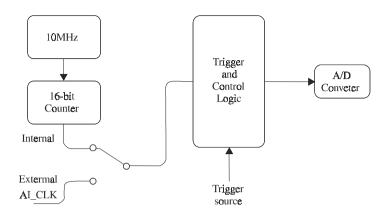

| Figure 5-5:  | PCI-1712/1732 Sample Clock Source                        | 38 |

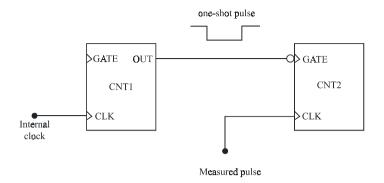

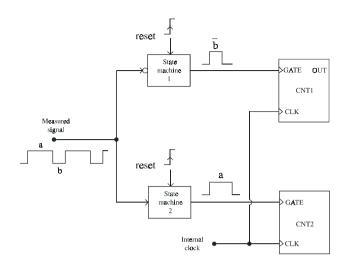

| Figure 5-6:  | Frequency measurement                                    | 49 |

| Figure 6-1:  | PCI-1712/1732 VR1 & TP5                                  | 55 |

| Figure 6-2:  | Selecting the device you want to calibrate               | 58 |

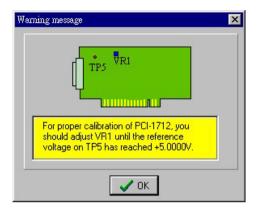

| Figure 6-3:  | Warning message before start calibration                 | 59 |

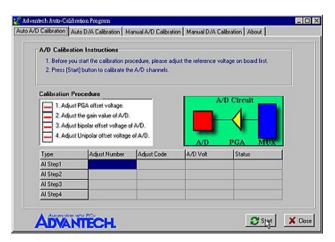

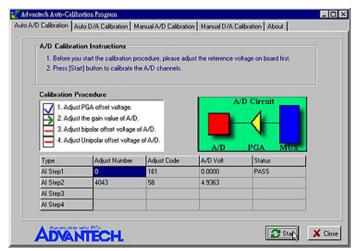

| Figure 6-4:  | Auto A/D Calibration Dialog Box                      | . 59 |

|--------------|------------------------------------------------------|------|

| Figure 6-5:  | A/D Calibration Procedure 1                          | . 60 |

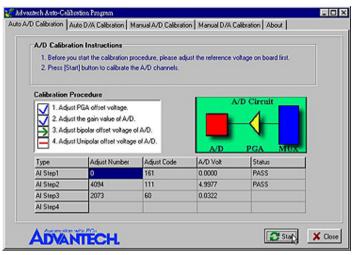

| Figure 6-6:  | A/D Calibration Procedure 2                          | . 60 |

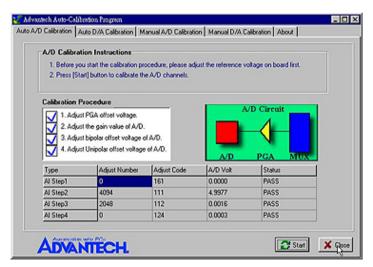

| Figure 6-7:  | A/D Calibration Procedure 3                          | . 61 |

| Figure 6-8:  | A/D Calibration is finished                          | . 61 |

| Figure 6-9:  | Range Selection in D/A Calibration                   | . 62 |

| Figure 6-10: | Calibrating D/A Channel 0                            | . 62 |

| Figure 6-11: | Calibrating D/A Channel 1                            | . 63 |

| Figure 6-12: | D/A Calibration is finished                          | 63   |

| Figure 6-13: | Selecting Input Rage in Manual A/D Calibration panel | . 64 |

| Figure 6-14: | Adjusting registers                                  | . 65 |

| Figure 6-15: | Selecting D/A Range and                              | . 66 |

| Figure 6-16: | Selecting D/A Range and                              | . 66 |

| Figure 6-17: | Adjusting registers                                  | . 67 |

| Figure C-1:  | PCLD-8712 board layout                               | . 75 |

| Figure C-2:  | CN2 pin assignments for the PCLD-8712                | . 76 |

# **Tables**

| Table 2.4.   | 1/O Compositor Circul Description (Dort 1)             | 04   |

|--------------|--------------------------------------------------------|------|

| Table 3-1:   | I/O Connector Signal Description (Part 1)              |      |

| Table 3-1:   | I/O Connector Signal Description (Part 2)              |      |

| Table 3-1:   | I/O Connector Signal Description (Part 3)              |      |

| Table 5-1:   | Gains and Analog Input Range                           | . 33 |

| Table 5-2:   | Analog Input Data Format                               | . 39 |

| Table 5-3:   | The corresponding Full Scale values for various Input  |      |

|              | Voltage Ranges                                         | . 39 |

| Table 5-4:   | Analog Output Data Format                              | . 43 |

| Table 5-5:   | The corresponding Full Scale values for various Output |      |

|              | Voltage Ranges                                         | . 43 |

| Table D-1:   | PCI-1712/1732 register format (Part 1)                 | . 80 |

| Table D-1:   | PCI-1712/1732 register format (Part 2)                 | . 81 |

| Table D-1:   | PCI-1712/1732 register format (Part 3)                 | . 82 |

| Table D-2:   | Register for channel number and A/D data               | . 83 |

| Table D-3:   | Register for A/D channel range setting                 | . 84 |

| Table D-4:   | Gain Codes for the PCI-1712/1732                       | . 85 |

| Table D-5:   | Register for multiplexer control                       | . 85 |

| Table D-6:   | Register for A/D control/status                        | . 87 |

| Table D-7:   | Analog Input Acquisition Mode                          | . 88 |

| Table D-8:   | Register for clear interrupt and FIFO                  | . 89 |

| Table D-9:   | Register for interrupt and FIFO status                 | . 90 |

| Table D-10:  | Register for D/A control                               | . 91 |

| Table D-11:  | Analog output operation mode                           | . 92 |

| Table D-12:  | Register for D/A channel 0/1 data                      | . 93 |

| Table D-13:  | Register for 82C54 counter chip 0                      | . 94 |

| Table D-14:  | Register for 82C54 counter chip 1                      | . 95 |

| Table D-15:  | Register for counter gate and clock control/status     | . 96 |

| Table D-16 : | Table of Cn1 to Cn0 register                           | . 96 |

| Table D-17:  | Table of Gn1 to Gn0 register                           | . 97 |

| Table D-18:  | Table for CLK_SEL1 to CLK_SEL0 register                | . 99 |

| Table D-19: | Register for Digital I/O               | 99    |

|-------------|----------------------------------------|-------|

| Table D-20: | Register for digital I/O configuration | . 100 |

| Table D-21: | Register for digital I/O configuration | . 100 |

| Table D-22: | Register for calibration command       | . 100 |

| Table D-23: | Calibration command                    | . 101 |

| Table D-24: | Register for D/A channel data          | . 102 |

## 1. Introduction

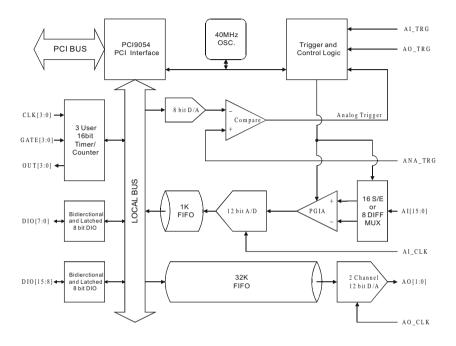

Thank you for buying the Advantech PCI-1712/1732 PCI card. The PCI-1712/1732 is a powerful high-speed multifunction DAS card for PCI bus. It features a 1MHz 12-bit A/D converter, an on-board FIFO buffer (storing up to 1K samples for A/D, and up to 32K samples for D/A conversion). The PCI-1712/1732 provides a total of up to 16 *single-ended* or 8 *differential A/D input channels* or a mixed combination, 2 *12-bit D/A output channels*, 16 *digital input/output channels*, and 3 *10MHz 16-bit multifunction counter channels*. PCI-1712/1732 provides specific functions for different user requirments:

## PCI-1712 1 MS/s High-Speed Multifunction Card

## PCI-1732 1 MS/s High-Speed Multifunction Card w/o analog output

The following sections of this chapter will provide further information about features of the DAS card, a Quick Start for installation, together with some brief information on software and accessories for the PCI-1712/1732 card.

## 1.1 Features

The Advantech PCI-1712/1732 provides users with the most requested measurement and control functions as seen below:

- Deci-bus mastering for data transfer

- □ 16 single-ended or 8 differential or combination analog inputs

- □ 12-bit A/D converter, with up to 1 MHz sampling rate

- Pre-, post-, about- and delay-trigger data acquisition modes for analog input channels

- Programmable gain for each analog input channel

- Automatic channel/gain/SD/BU scanning

- □ On-board FIFO buffer storing up to 1K samples for A/D and 32K samples for D/A

- □ Two 12-bit analog output channels with continuous waveform output function

- □ Auto calibration for analog input and output channels

- □ 16 digital Input and output channels

- □ Three 16-bit programmable multifunction counters/timers on 10MHz clock.

The Advantech PCI-1712 offers the following main features:

### **PCI-Bus Mastering Data Transfer**

The PCI-1712/1732 supports *PCI-Bus mastering DMA* for high-speed data transfer and gap-free analog input and analog output. By setting aside a block of memory in the PC, the PCI-1712/1732 performs bus-mastering data transfers without CPU intervention, setting the CPU free to perform other more urgent tasks such as data analysis and graphic manipulation. The function allows users to run all I/O functions simultaneously at full speed without losing data.

#### **Plug-and-Play Function**

The PCI-1712/1732 is a Plug-and-Play device, which fully complies with the PCI Specification Rev 2.2. During card installation, you have no need to set any jumpers or DIP switches. Instead, all bus-related configurations such as base I/O address and interrupt are automatically done by the Plug-and-Play function.

## **On-board FIFO Memory**

The PCI-1712/1732 provides an *on-board FIFO* (First In First Out) memory buffer, storing up to 1K samples for A/D and 32K for D/A conversion (PCI-1712 only).

#### Automatic Channel/Gain/SD\*/BU\* Scanning

PCI-1712/1732 features an *automatic channel/Gain/SD/BU scanning circuit*. This circuit controls multiplexer switching during sampling in a way that is much more efficient than software implementation. *Onboard SRAM* stores different gain, SD and BU values for each channel. This combination lets user perform multi-channel high-speed sampling with different gain, SD and BU values for each channel. SD: Single-Ended/Differential Analog Input

BU: Bipolar/Unipolar

## Flexible Triggering and Clocking Capabilities

The PCI-1712/1732 provides flexibility in triggering action, both in the available trigger modes and trigger events for analog input. You can acquire data using *post-trigger, pre-trigger, delay-trigger* and *about-trigger* modes. The trigger source could be either analog or digital signal. The analog trigger could originate from a dedicated input pin. In fact, you can designate any of the analog input channels as the analog trigger input. You can also set the analog trigger level within a voltage range from zero to A/D FSR. When trigger signal being digital, you can pace A/D and D/A conversion using software interrupt, internal or external clock.

PCI-1712/1732 User's Manual

#### **Continuous Analog Output**

The PCI-1712 provides two analog output channels. Both of them can perform continuous waveform output. The analog output can be up to 500kS/s for each analog output channel. Or you can load a cyclic waveform into an on-board FIFO, which will continuously output the cyclic waveform. The on-board FIFO of the PCI-1712 can store 2 to 32K samples for the waveform output.

#### **On-board Programmable Multifunction Counter/Timer**

The PCI-1712/1732 is equipped with three programmable multifunction counters/timers, which can serve as a *pacer trigger* for A/D conversion. The counter chip is an 82C54 or equivalent, which incorporates three 16-bit channels on a 10 MHz clock. And then we enhance the gate and clock input function for more applications, of event counting, pulse generation, duty cycle frequency generation, one shot, frequency measurement and pulse width measurement.

#### Note:

- Pace trigger determines how fast A/D conversion will be done in pacer trigger mode.

- Solution Not Series Series

## **1.2 Installation Guide**

Before you install your PCI-1712/1732 card, please make sure you have the following necessary components:

#### Deci-1712/1732 DAS card

#### Deci-1712/1732 User's Manual

| Driver software | Advantech DLL drivers<br>(included in the companion CD-ROM) |

|-----------------|-------------------------------------------------------------|

| Wiring cable    | PCL-10168                                                   |

| Wiring board    | PCLD-8712, ADAM-3968                                        |

| Computer        | Personal computer or workstation with a PCI-bus slot        |

Some other optional components are also available for enhanced operation:

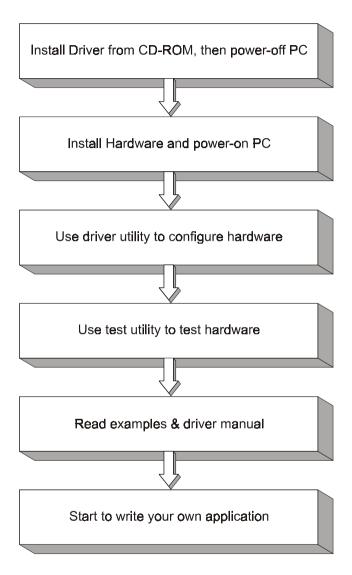

Figure 1-1: Installation Flow Chart

□ Application software ActiveDAQ, GeniDAQ or other third-party software packages

After you have got the necessary components and maybe some accessories for enhanced operation of your DAS card, you can then begin the Installation procedures. Figure 1-1 on the next page provides a concise flow chart to give users a broad picture of the software and hardware installation procedures:

## **1.3 Accessories**

Advantech offers a complete set of accessory products to support the PCI-1712/1732 cards. These accessories include:

#### Wiring Cable

□ PCL-10168 The PCL-10168 shielded cable is specially designed for PCI-1712/1732 card to provide higher resistance to noise. To achieve a better signal quality, the signal wires are twisted in such a way as to form a twisted-pair cable, reducing crosstalk and noise from other signal sources. Furthermore, its analog and digital lines are separately sheathed and shielded to neutralize EMI/EMC problems.

#### Wiring Boards

- □ ADAM-3968 The ADAM-3968 is a 68-pin SCSI wiring terminal module for DIN-rail mounting. This terminal module can be readily connected to the Advantech PC-Lab cards and allow easy yet reliable access to individual pin connections for the PCI-1712/1732 card.

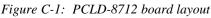

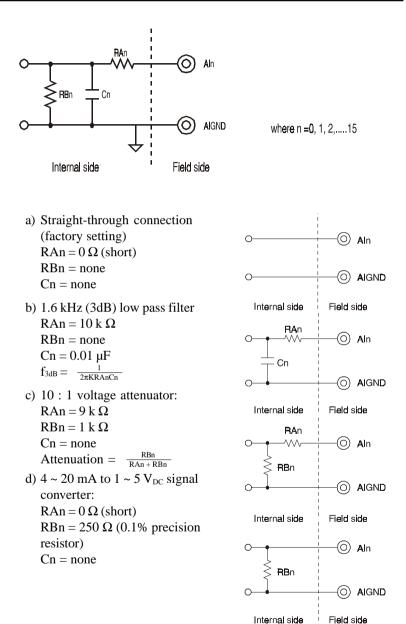

- **PCLD-8712** The PCLD-8712 is a DIN-rail mounting screwterminal board to be used with any of the PC-LabCards which have 68-pin SCSI connectors. The PCLD-8712 features the following functions:

- One additional 20-pin flat-cable connectors for digital input and output

- Reserved space on the board to meet future needs for signalconditioning circuits (low-pass filter, voltage attenuator and current shunt)

#### Chapter 1

• Industrial-grade screw-clamp terminal blocks for heavy-duty and reliable connections.

# 2. Installation

This chapter gives users a package item checklist, proper instructions about unpacking and step-by-step procedures for both driver and card installation.

## 2.1 Unpacking

After receiving your PCI-1712/1732 package, please inspect its contents first. The package should contain the following items:

PCI-1712/1732 card

Companion CD-ROM (DLL driver included)

☑ User's Manual

Ouick Start

The PCI-1712/1732 card harbors certain electronic components vulnerable to *electrostatic discharge* (ESD). ESD could easily damage the integrated circuits and certain components if preventive measures are not carefully paid attention to. *Before removing the card from the* antistatic plastic bag, you should take following precautions to ward off possible ESD damage:

- Touch the metal part of your computer chassis with your hand to discharge static electricity accumulated on your body. Or one can also use a grounding strap.

- Touch the antistatic bag to a metal part of your computer chassis before opening the bag.

- Take hold of the card only by the metal bracket when removing it out of the bag.

#### After taking out the card, first you should:

• Inspect the card for any possible signs of external damage (loose or damaged components, etc.). If the card is visibly damaged, please notify our service department or our local sales representative immediately. Avoid installing a damaged card into your system.

#### Also pay extra caution to the following aspects to ensure proper installation:

Avoid physical contact with materials that could hold static electricity such as plastic, vinyl and Styrofoam.

Whenever you handle the card, grasp it only by its edges. DO NOT TOUCH the exposed metal pins of the connector or the electronic components.

#### Note:

★ Keep the antistatic bag for future use. You might need the original bag to store the card if you have to remove the card from PC or transport it elsewhere.

## 2.2 Driver Installation

We recommend you to install the driver before you install the PCI-1712/1732 card into your system, since this will guarantee a smooth installation process.

The 32-bit DLL driver Setup program for the card is included on the companion CD-ROM that is shipped with your DAS card package. Please follow the steps below to install the driver software:

Step 1: Insert the companion CD-ROM into your CD-ROM drive.

**Step 2:** The Setup program will be launched automatically if you have the autoplay function enabled on your system. When the Setup Program is launched, you'll see the following Setup Screen.

#### Note:

▲ If the autoplay function is not enabled on your computer, use Windows Explorer or Windows *Run* command to execute SETUP.EXE on the companion CD-ROM.

Figure 2-1: The Setup Screen of Advantech Automation Software

PCI-1712/1732 User's Manual

Step 3: Select the *DLL Drivers* option.

**Step 4:** Select the *Windows 95/98* or *Windows NT* option according to your operating system. Just follow the installation instructions step by step to complete your DLL driver setup.

#### Figure 2-2: Different options for Driver Setup

For further information on driver-related issues, an online version of *DLL Drivers Manual* is available by accessing the following path:

Start/Programs/Advantech Driver for 95 and 98 (or for NT)/Driver Manual

## 2.3 Hardware Installation

#### Note:

Make sure you have installed the driver first before you install the card (please refer to 2.2 Driver Installation)

After the DLL driver installation is completed, you can now go on to install the PCI-1712/1732 card in any PCI slot on your computer. But it is suggested that you should refer to the computer user manual or related documentations if you have any doubt. Please follow the steps below to install the card on your system.

Step 1: Turn off your computer and unplug the power cord and cables.

TURN OFF your computer before installing or removing any components on the computer.

- Step 2: Remove the cover of your computer.

- Step 3: Remove the slot cover on the back panel of your computer.

- **Step 4**: Touch the metal part on the surface of your computer to neutralize the static electricity that might be on your body.

- **Step 5**: Insert the PCI-1712/1732 card into a PCI slot. Hold the card only by its edges and carefully align it with the slot. Insert the card firmly into place. Use of excessive force must be avoided, otherwise the card might be damaged.

- **Step 6**: Fasten the bracket of the PCI card on the back panel rail of the computer with screws.

- Step 7: Connect appropriate accessories (68-pin cable, wiring terminals, etc. if necessary) to the PCI card.

- **Step 8**: Replace the cover of your computer chassis. Re-connect the cables you removed in step 2.

- Step 9: Plug in the power cord and turn on the computer .

#### Note:

▲ In case you installed the card without installing the DLL driver first, Windows 95/98 will recognize your card as an "unknown device" after reboot, and will prompt you to provide necessary driver. You should ignore the prompting messages (just click the *Cancel* button) and set up the driver according to the steps described in 2.2 Driver Installation.

After the PCI-1712/1732 card is installed, you can verify whether it is properly installed on your system in the *Device Manager*:

- 1. Access the *Device Manager* through *Control Panel/System/Device Manager*.

- 2. The *device name* of the PCI-1712/1732 should be listed on the *Device Manager* tab on the System *Property* Page.

Figure 2-3: The device name listed on the Device Manager

#### Note:

▲ If your card is properly installed, you should see the *device name* of your card listed on the *Device Manager* tab. If you do see your device name listed on it but marked with an exclamation sign "!", it means your card has not been correctly installed. In this case, remove the card device from the *Device Manager* by selecting its device name and press the *Remove* button. Then go through the driver installation process again.

After your card is properly installed on your system, you can now configure your device using the *Device Installation* Program that has itself already been installed on your system during driver setup. A complete device installation procedure should include *device setup*, *configuration* and *testing*. The following sections will guide you through the Setup, Configuration and Testing of your device.

## 2.4 Device Setup & Configuration

The *Device Installation* program is a utility that allows you to set up, configure and test your device, and later stores your settings on the system registry. These settings will be used when you call the APIs of Advantech 32-bit DLL drivers.

#### Setting Up the Device

Step 1: To install the I/O device for your card, you must first run the Device Installation program (by accessing Start/Programs/ Advantech Driver for 95 and 98 (or for NT)/Device Installation).

Figure 2-4: The Advantech Device Installation utility program

Step 2: On the *Device Installation* program window, select the *Device* menu item on the menu bar, and click the *Setup* command (Fig. 2-4) to bring up the *I/O Device Installation* dialog box (Fig. 2-5). You can then view the device(s) already installed on your system (if any) on the *Installed Devices* list box.

| Advantech IO Device Installation                                                                                           | ×                             |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Installed Devices:                                                                                                         |                               |

| - 🔚 My Computer                                                                                                            | Setup<br>Romove<br>Iest<br>OK |

| List of Device:<br>Advanteh PCI-1710HG<br>Advanteh PCI-1711<br>Advanteh PCI-1712<br>Advanteh PCI-1713<br>Advanteh PCI-1713 |                               |

Figure 2-5: The I/O Device Installation dialog box

Step 3: Scroll down the *List of Devices* box to find the device that you wish to install, then click the *Add* button to evoke the *Device(s) Found* dialog box such as one shown in Fig. 2-6. The *Device(s) Found* dialog box lists all the installed devices on your system. Select the device you want to configure from the list box and press the *OK* button. After you have clicked *OK*, you will see a *Device Setting* dialog box such as the one in Fig. 2-7.

| Advantech PCI-1712 device(s) found                                 | ×      |

|--------------------------------------------------------------------|--------|

| List below is how many PCI-1712 cards on<br>Please select one from |        |

| Device<br>PCI-1712 Slot= 0 1/0= 6600H IRQ= 1                       | ок     |

|                                                                    | Cancel |

Figure 2-6: The "Device(s) Found" dialog box

#### **Configuring the Device**

**Step 4:** On the *Device Setting* dialog box (Fig. 2-7), you can configure the parameters of A/D, D/A, DIO and Counter functions.

| PCI-1712 Device Setting                                                | ×                                                                                               |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Base Address : 6600 Hex<br>A/D Channels Configuration<br>Channel : 0 • | Interrupt Channel C<br>D/A Voltage Ref - Channel 0<br>C External © Internal<br>Voltage : 0 ~ 5V |

| C Differential                                                         | D/A Voltage Ref - Channel 1<br>C External ⓒ Internal                                            |

| Freq. measurement area                                                 | Voltage : 0 ~ 5V                                                                                |

| Pulse width measurement area                                           | Low byte IN                                                                                     |

| <u>OK</u> <u>C</u> ancel                                               | Help About                                                                                      |

Figure 2-7: The Device Setting dialog box

#### Note:

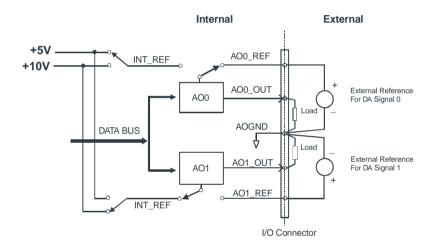

Solution N Users can configure the source of D/A reference voltage either as Internal or External, and then select for the unipolar or the bipolar output voltage range. When selecting voltage source as *Internal*, users will have options for the output voltage ranges :  $0 \sim 5V$  and  $0 \sim 10V$  for *unipolar*;  $-5 \sim 5V$  and  $-10 \sim 10V$  for *bipolar*. When selected as *External*, the output voltage range is determined by the external reference voltage in the following way : By inputting an external reference voltage: xV, where 0 <= x <= 10, you will get a output voltage range: 0 to xV for *unipolar*; *and* -x to xV for *bipolar*

**Step 5**: After you have finished configuring the device, click *OK* and the *device name* will appear in the *Installed Devices* box as seen below:

Figure 2-8: The Device Name appearing on the list of devices box

#### Note:

▲ As we have noted, the *device name* "000:PCI-1712 I/O=6600H" begins with a *device number* "000", which is specifically assigned to each card cifically. The *device number* is passed to the driver to specify which device you wish to control.

If you want to test the card device further, go right to the next section on the *Device Testing*.

## 2.5 Device Testing

Following through the *Setup* and *Configuration* procedures to the last step described in the previous section, you can now proceed to test the device by clicking the *Test* Button on the *I/O Device Installation* dialog box (Fig. 2-8). A *Device Test* dialog box will appear accordingly:

| Advantech Device Test - 00 🎜 | ) : {PCI-1' | 712 I/O=6600H}    |                    | _ 🗆 ×            |

|------------------------------|-------------|-------------------|--------------------|------------------|

| Analog input Analog          | output      | Digital input     | Digital output     | Cou <u>n</u> ter |

| Channel No. Input range:     |             | Analog input read |                    |                  |

| 0 0.10V                      | -           | 0.0000000         | Channel mode       |                  |

| 1 0-10V                      | -           | 0.0000000         | 16 single ended o  | hannels          |

| 2 0-10V                      | •           | 0.0000000         | Sampling period: 1 | )00 ms           |

| 3 0-10V                      | -           | 0.0000000         | •                  | Þ                |

| 4 0-10V                      | •           | 0.0000000         |                    |                  |

| 5 0-10V                      | -           | 0.0000000         |                    |                  |

| 6 0-10V                      | -           | 0.0000000         |                    |                  |

| 7 0-10V                      | •           | 0.0000000         |                    |                  |

|                              |             |                   | Change device      | Exit             |

Figure 2-9: Analog Input tab on the Device Test dialog box

On the *Device Test* dialog box, users are free to test various functions of PCI-1712/1732 on the *Analog input, Analog output, Digital input, Digital output* or *Counter* tabs.

#### Note:

You can access the Device Test dialog box either by the previous procedure for the Device Installation Program or simply by accessing Start/Programs/Advantech Driver for 95 and 98 (or for NT) /Test Utility.

#### **Testing Analog Input Function**

Click the *Analog Input* tab to bring it up to front of the screen. Select the input range for each channel in the *Input range* drop-down boxes. Configure the sampling rate on the scroll bar. Switch the channels by using the up/down arrow.

| ॢ 🗐 Advantech Devic | e Test - 000 : {PCI-17 | 12 I/O=6600H}      |                  | _ 🗆 X            |

|---------------------|------------------------|--------------------|------------------|------------------|

| Analog input        | Analog <u>o</u> utput  | Digital input      | Digital output   | Cou <u>n</u> ter |

| Channel No. Ir      | nput range:            | Analog input readi |                  |                  |

| 0 0.1               | 0V 💌                   | 0.0000000          | Channel mode —   |                  |

| 1 0.1               | OV 💌                   | 0.0000000          | 16 single ended  | channels         |

| 2 0-1               | OV 💌                   | 0.0000000          | Sampling period: | 1000 ms          |

| 3 0-1               | 0V 💌                   | 0.0000000          |                  | ▶                |

| 4 0.1               | OV 💌                   | 0.0000000          |                  |                  |

| 5 0-1               | 0V 💌                   | 0.0000000          |                  |                  |

| 6 0.1               | 0V 💌                   | 0.0000000          |                  |                  |

| 7 0-1               | ov 💌                   | 0.0000000          |                  |                  |

|                     |                        |                    |                  |                  |

|                     |                        |                    | Change device    | Egit             |

Figure 2-10: Analog Input tab on the Device Test dialog box

#### Testing Analog Output Function (PCI-1712 only)

Click the *Analog Output* tab to bring it up to the foreground. The *Analog Output* tab allows you to output quasi-sine, triangle, or square waveforms generated by the software automatically, or output single values manually. You can also configure the waveform frequency and output voltage range.

| Advantech Device Test - 000 : (PCI-171                                 | 2 I/O=6600H}  |                      | _ 🗆 ×                                                                        |

|------------------------------------------------------------------------|---------------|----------------------|------------------------------------------------------------------------------|

| Analog input Analog output                                             | Digital input | Digital output       | Counter                                                                      |

|                                                                        | Manual Output | Output voltage       | Waveform out is<br>generated by<br>software with 100<br>points in one cycle. |

| Channel 1<br>Waveform output<br>05 ±V<br>Overall waveform period: 10 a | Manual Output | Output voltage<br>O↓ |                                                                              |

|                                                                        |               | Change device        | Egit                                                                         |

Figure 2-11: Analog Output tab on the Device Test dialog box

#### **Testing Digital Input Function**

Click the *Digital Input* tab to show forth the *Digital Input* test panel as seen below. Through the color of the lamps, users can easily discern whether the status of each digital input channel is either high or low.

Figure 2-12: Digital Input tab on the Device Test dialog box

#### **Testing Digital Output Function**

Click the *Digital Output* tab to bring up the *Digital Output* test panel such as seen on the next page. By pressing the buttons on each tab, users can easily set each digital output channel as *high* or *low* for the corresponding port.

| "Advantech Device Test - 0 |                           |                  | _ 🗆 🗙               |

|----------------------------|---------------------------|------------------|---------------------|

| Analog input Analo         | g <u>o</u> utput │ Digita | input Digital o  | stput Counter       |

| Port No. Bit 7             | 4 3                       | 0 Hex            | On(1)               |

|                            |                           |                  | Off(0)              |

|                            |                           |                  | _                   |

|                            |                           |                  |                     |

|                            |                           |                  |                     |

|                            |                           |                  |                     |

|                            |                           |                  |                     |

|                            |                           | <u>C</u> hange d | evice E <u>v</u> it |

Figure 2-13: Digital Output tab on the Device Test dialog box

#### **Testing Counter Function**

Click the *Counter* Tab to bring its test panel forth. In the test utility, the counter channel (*Channel 0*) offers the users two options: *Event counting* and *Pulse out*. If you select *Event counting*, you need first to connect your clock source to pin CNT0\_CLK, and the counter will start counting after the pin CNT0\_GATE is triggered. If you select *Pulse Out*, the clock source will be output to pin CNT0\_OUT. You can

| 🦪 Advantech Devic                                   | e Test - 000 : {PCI-17: | 2 I/O=6600H}                       |                | _ 🗆 ×            |

|-----------------------------------------------------|-------------------------|------------------------------------|----------------|------------------|

| Analog input                                        | Analog <u>o</u> utput   | Digital input                      | Digital output | Cou <u>n</u> ter |

| Channel<br>Sampling r.<br>Counting v<br>Pulse frequ | ate: 500ms<br>alue: 0   | Event countin<br>Pulse out<br>Stop |                |                  |

|                                                     |                         |                                    |                |                  |

|                                                     |                         |                                    |                | <b>V</b>         |

|                                                     |                         |                                    | Change device  | Eyit             |

configure the *Pulse Frequency* by the scroll bar right below it.

Figure 2-14: Digital output tab on the Device Test dialog box

Only after your card device is properly set up, configured and tested, can the device installation procedure be counted as complete. After the device installation procedure is completed, you can now safely proceed to the next chpater, *Signal Connections*.

# 3. Signal Connections

## 3.1 Overview

Maintaining proper signal connections is one of the most important factors to ensure that your application system is sending and receiving data correctly. A good signal connection can avoid unnecessary and costly damage to your PC and other hardware devices. This chapter provides useful information about how to connect input and output signals to the PCI-1712/1732 via the I/O connector.

## 3.2 I/O Connector

The I/O connector on the PCI-1712/1732 is a 68-pin connector that enables you to connect to accessories with the PCL-10168 shielded cable.

#### Note:

➤ The PCL-10168 shielded cable is especially designed for the PCI-1712/ 1732 to reduce noise in the analog signal lines. Please refer to Section 1.3 Accessories.

#### **Pin Assignment**

Figure 3-1 shows the pin assignments for the 68-pin I/O connector on the PCI-1712/1732, and table 3-1 lists the detailed illustration of the pins.

#### Note:

➤ The three ground references AIGND, AOGND, and DGND should be used discreetly each according to its designated purpose.

|              | ſ          |    |               |  |  |

|--------------|------------|----|---------------|--|--|

| Alû          | 68         | 34 | <b>A</b> I1   |  |  |

| <b>A</b> I2  | 67         | 33 | <b>AI</b> 3   |  |  |

| Al4          | 66         | 32 | <b>A</b> I5   |  |  |

| Al6          | <b>6</b> 5 | 31 | <b>A</b> I7   |  |  |

| Al8          | 64         | 30 | Al9           |  |  |

| Al10         | <b>6</b> 3 | 29 | <b>Al</b> 11  |  |  |

| <b>Al</b> 12 | 62         | 28 | <b>Al</b> 13  |  |  |

| Al14         | 61         | 27 | <b>Al</b> 15  |  |  |

| AIGND        | 60         | 26 | ANA_TRG       |  |  |

| AO0_REF*     | 5 <b>9</b> | 25 | AO1_REF*      |  |  |

| AO0_OUT*     | 58         | 24 | AO1_OUT*      |  |  |

| AOGND*       | 57         | 23 | AOGND*        |  |  |

| AI_CLK*      | 56         | 22 | AI_TRG*       |  |  |

| DGND         | 55         | 21 | DGND          |  |  |

| AO_CLK*      | 54         | 20 | AO_TRG*       |  |  |

| CNTO_CLK     | 53         | 19 | CNT0_GATE     |  |  |

| CNTO_OUT     | 52         | 18 | DGND          |  |  |

| CNT1_CLK     | 51         | 17 | CNT1_GATE     |  |  |

| CNT1_OUT     | 50         | 16 | DGND          |  |  |

| CNT2_CLK     | 49         | 15 | CNT2_GATE     |  |  |

| CNT2_OUT     | 48         | 14 | DGND          |  |  |

| DIO0         | 47         | 13 | DIO1          |  |  |

| DIO2         | 46         | 12 | DIO3          |  |  |

| DIO4         | 45         | 11 | DIO5          |  |  |

| DIO6         | 44         | 10 | DIÓ7          |  |  |

| DGND         | 43         | 9  | DGND          |  |  |

| DIO8         | 42         | 8  | DIO9          |  |  |

| DIO10        | 41         | 7  | DIO11         |  |  |

| DIO12        | 40         | 6  | DIO13         |  |  |

| DIO14        | 39         | 5  | <b>DIO</b> 15 |  |  |

| DGND         | 38         | 4  | DGND          |  |  |

| AI TRG OUT   | 37         | 3  | AI TRG OUT    |  |  |

| NC           | 36         | 2  | NC            |  |  |

| +12V         | 35         | 1  | +5V           |  |  |

|              |            |    |               |  |  |

|              | L          |    |               |  |  |

|              |            |    |               |  |  |

|              |            |    |               |  |  |

Figure 3-1: I/O connector pin assignments for the PCI-1712/1732 \*: Pins 20, 22~25, 54, 56~59 are not defined on PCI-1732

### I/O Connector Signal Description

| Signal Name | Reference | Direction | Description                                                                                                                                                                                                                                                                    |

|-------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Al<015>     | AIGND     | Input     | Analog Input Channels 0 through 15.<br>Each channel pair, Al <i, i+8=""> (i = 07),<br/>can be configured as either one<br/>differential input or two single-ended<br/>inputs.</i,>                                                                                             |

| AIGND       | -         | -         | Analog Input Ground. These pins are<br>the reference points for single-ended<br>measurements and the bias current<br>return point for differential<br>measurement. All three ground<br>references ? AIGND, AOGND and<br>DGND ? are connected together on<br>the PCI-1712 card. |

| AO0_REF     | AOGND     | Input     | Analog Channel 0 Output External<br>Reference. This is the external<br>reference input for the analog output<br>channel 0 circuitry.                                                                                                                                           |

| AO1_REF     | AOGND     | Input     | Analog Channel 1 Output External<br>Reference. This is the external<br>reference input for the analog output<br>channel 1 circuitry.                                                                                                                                           |

| ANA_TRG     | AIGND     | Input     | Analog threshold Trigger. This pin is the analog input threshold trigger input.                                                                                                                                                                                                |

| AO0_OUT     | AOGND     | Output    | Analog Channel 0 Output. This pin<br>supplies the voltage output of analog<br>output channel 0.                                                                                                                                                                                |

| AO1_OUT     | AOGND     | Output    | Analog Channel 1 Output. This pin<br>supplies the voltage output of analog<br>output channel 1.                                                                                                                                                                                |

| AI_CLK      | DGND      | Input     | Analog Input external clock input.<br>This is the external clock input for the<br>analog input.                                                                                                                                                                                |

| AI_TRG      | DGND      | Input     | Analog Input TTL Trigger-This is the TTL trigger for analog trigger.                                                                                                                                                                                                           |

| AOGND       | -         | -         | Analog Output Ground. The analog<br>output voltages are referenced to<br>theses nodes. All three ground<br>references ? AIGND, AOGND, and<br>DGND ? are connected together on<br>your PCI-1712 card.                                                                           |

#### Table 3-1: I/O Connector Signal Description (Part 1)

## Chapter 3

| Signal Name | Reference | Direction | Description                                                                                                                                                                                                                           |

|-------------|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIO<015>    | DGND      | Input     | <b>Digital Input / Output signals.</b> These pins are digital input / output channel 0 to 15                                                                                                                                          |

| AI_CLK      | DGND      | Input     | Analog Input external clock input.<br>This is the external clock input for the<br>analog input.                                                                                                                                       |

| AI_TRG      | DGND      | Input     | <b>Analog Input TTL Trigger</b> - This is the TTL trigger for analog trigger.                                                                                                                                                         |

| AI_CLK_OUT  | DGND      | Output    | Analog Input Clock Output. This pin<br>pulses once for each pacer clock. This<br>signal serves as a synchronous signal<br>for application. The low-to-high edge<br>start A/D conversion.                                              |

| AI_TRG_OUT  | DGND      | Output    | Analog Input Trigger Output. This pin<br>outputs the analog input trigger signal.<br>The low-to-high edge indicates the<br>trigger event.                                                                                             |

| DGND        | -         | -         | <b>Digital Ground.</b> This pin supplies the reference for the digital signals at the I/O connector as well as the +5VDC supply. All three ground references ? AIGND, AOGND, and DGND ? are connected together on your PCI-1712 card. |

Table 3-1: I/O Connector Signal Description (Part 2)

| Signal Name | Reference | Direction | Description                                                                                                                                         |

|-------------|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| CNT0_CLK    | DGND      | Input     | <b>Counter 0 Clock Input.</b> This pin is the counter 0 external clock input (up to 10MHz), counter 0 clock can be either internal set by software. |

| CNT0_GATE   | DGND      | Input     | <b>Counter 0 Gate Input.</b> This pin is for counter 0 gate control, see 82C54 data sheet for detailed information.                                 |

| CNT0_OUT    | DGND      | Output    | <b>Counter 0 Output.</b> This pin is counter 0 output, see 82C54 data sheet for detailed information.                                               |

| CNT1_CLK    | DGND      | Input     | <b>Counter 1 Clock Input.</b> This pin is the counter 1 external clock input (up to 10MHz), counter 1 clock can be either internal set by software. |

| CNT1_GATE   | DGND      | Input     | <b>Counter 1 Gate Input.</b> This pin is for counter 1 gate control, see 82C54 data sheet for detailed information.                                 |

| CNT1_OUT    | DGND      | Output    | <b>Counter 1 Output.</b> This pin is counter 1 output, see 82C54 data sheet for detailed information.                                               |

| CNT2_CLK    | DGND      | Input     | <b>Counter 2 Clock Input.</b> This pin is the counter 2 external clock input (up to 10MHz), counter 2 clock can be either internal set by software. |

| CNT2_GATE   | DGND      | Input     | <b>Counter 2 Gate Input.</b> This pin is for counter 2 gate control, see 82C54 data sheet for detailed information.                                 |

| CNT2_OUT    | DGND      | Output    | <b>Counter 2 Output.</b> This pin is counter 2 output, see 82C54 data sheet for detailed information.                                               |

| +12V        | DGND      | Output    | +12 VDC Source. This pin is +12V power supply.                                                                                                      |

| +5V         | DGND      | Output    | +5 VDC Source. This pin is +5 V power supply.                                                                                                       |

| NC          | -         | -         | No Connection. These pins serve no connection.                                                                                                      |

Table 3-1:

I/O Connector Signal Description (Part 3)

## 3.3 Analog Input Connections

The PCI-1712/1732 supports either 16 single-ended or 8 differential analog inputs. Each individual input channel is software-selected.

#### **Single-ended Channel Connections**

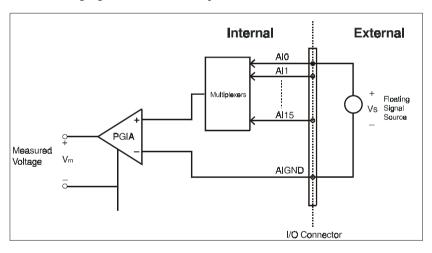

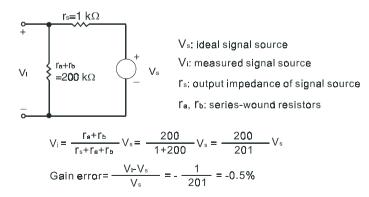

The single-ended input configuration has only one signal wire for each channel, and the *measured voltage* (Vm) is the voltage of the wire as referenced against the common ground.

A signal source without a local ground is also called a "floating source". It is fairly simple to connect a single-ended channel to a floating signal source. In this mode, the PCI-1712/1732 provides a reference ground for external floating signal sources.

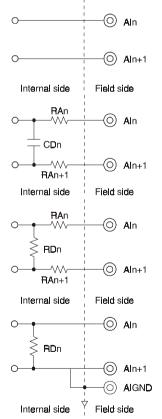

Figure 3-2 shows a single-ended channel connection between a floating signal source and an input channel on the PCI-1712/1732.

Figure 3-2: Single-ended input channel connection

#### **Differential Channel Connections**

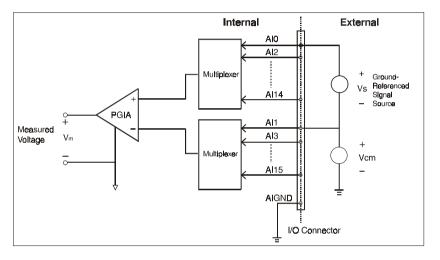

The differential input channels operate with two signal wires for each channel, and the voltage difference between both signal wires is measured. On the PCI-1712/1732, when all channels are configured to differential input, up to 8 analog channels are available.

If one side of the signal source is connected to a local ground, the signal source is ground-referenced. Therefore, the ground of the signal source and the ground of the card will not be exactly of the

same voltage. The difference between the ground voltages forms a common-mode voltage ( $V_{cm}$ ).

To avoid the ground loop noise effect caused by common-mode voltages, you can connect the signal ground to the Low input. Figure 3-3 shows a differential channel connection between a ground-reference signal source and an input channel on the PCI-1712/1732. With this connection, the PGIA rejects a common-mode voltage  $V_{\rm cm}$  between the signal source and the PCI-1712/1732 ground, shown as  $V_{\rm cm}$  in Figure 3-3.

Figure 3-3: Differential input channel connection - ground reference signal source

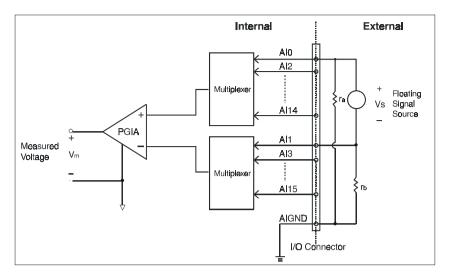

If a floating signal source is connected to the differential input channel, the signal source might exceed the common-mode signal range of the PGIA, and the PGIA will be saturated with erroneous voltage-readings. You must therefore reference the signal source against the AIGND.

Figure 3-4 shows a differential channel connection between a floating signal source and an input channel on the PCI-1712/1732. In this figure, each side of the floating signal source is connected through a resistor to the AIGND. This connection can reject the common-mode voltage between the signal source and the PCI-1712/1732 ground.

Figure 3-4: Differential input channel connection - floating signal source